Instruction Manual 40-385.4A V2.10

#### ABB Power T&D Company Inc.

Relay Divisions 4300 Coral Ridge Drive Coral Springs, FL 33065

305 752-6700 800 523-2620

September 1994

# **MDAR** Relay System (V2.10)

### **MDAR REVISION NOTICE**

| DATE  | REV LEVEL | PAGES REMOVED              | PAGES INSERTED |

|-------|-----------|----------------------------|----------------|

| 11/92 | Released  |                            |                |

| 9/94  | А         | ii, v, vi, vii, viii, & ix | same           |

|       |           | 2-11                       | 2-11 & 12      |

|       |           | 3-2, 6, & 9                | same           |

|       |           | 4-8, 17                    | same           |

|       |           | 5-8                        | same           |

|       |           | A-1, 2, 4, & 5             | same           |

|       |           | B-1, 2, 3, & 4             | same           |

|       |           | C-1, 4, 5, 6, & 7          | same           |

|       |           | D-1, 2, & 4                | same           |

|       |           | E-1, 4, 8, & 10            | same           |

|       |           | F-1, 4                     | same           |

|       |           | G-1, 3, 4, 5, 6, & 7       | same           |

|       |           | H-1, 3, & H-13, 14,        | same           |

|       |           | Index-1 to 6               | same           |

|       |           | J-1 to J-5                 | same           |

CHANGE SUMMARY:

A CHANGE BAR ( ) LOCATED IN THE MARGIN REPRESENTS A TECHNICAL CHANGE TO THE PRODUCT.

It is recommended that the user of MDAR equipment become acquainted with the information in this instruction leaflet before energizing the system. Failure to do so may result in injury to personnel or damage to the equipment, and may affect the equipment warranty. If the MDAR relay system is mounted in a cabinet, the cabinet must be bolted to the floor, or otherwise secured before MDAR installation, to prevent the system from tipping over.

All integrated circuits used on the modules are sensitive and can be damaged by the discharge of static electricity. Electrostatic discharge precautions should be observed when handling modules or individual components.

ABB does not assume liability arising out of the application or use of any product or circuit described herein. ABB reserves the right to make changes to any products herein to improve reliability, function or design. Specifications and information herein are subject to change without notice. All possible contingencies which may arise during installation, operation, or maintenance, and all details and variations of this equipment do not purport to be covered by these instructions. If further information is desired by purchaser regarding a particular installation, operation or maintenance of equipment, the local ABB representative should be contacted.

Copyright  $\bigcirc$  1990 – 1994 ABB Power T&D Company Inc .All Rights Reserved ABB may revise this publication from time to time without notice. Your right to copy this publication is limited by copyright law. Making copies without prior written authorization of ABB, is prohibited by law and constitutes a punishable violation of the law.

ABB does not convey any license under its patent rights nor the rights of others.

#### PREFACE

#### Scope

This manual describes the functions and features of the MDAR Relay System. It is intended primarily for use by engineers and technicians involved in the installation, testing, operation and maintenance of the MDAR system.

#### **Equipment Identification**

The MDAR equipment is identified by the Catalog Number on the MDAR chassis nameplate. The Catalog Number can be decoded by using Catalog Number Table 3-1 (see Section 3).

#### **Production Changes**

When engineering and production changes are made to the MDAR equipment, a revision notation (SUB #) is reflected on the appropriate schematic diagram, and associated parts information. A summary of all Sub #s for the particular release is shown below.

#### **Equipment Repair**

Repair work is done most satisfactorily at the factory. When returning equipment, carefully pack modules and other units, etc. All equipment should be returned in the original packing containers if possible. Any damage due to improperly packed items will be charged to the customer.

#### **Document Overview**

The circuitry is divided into 6 standard modules and one option module. Section 1 provides the Product Description, which includes software functions. [Appendices A through G include related module circuit descriptions.] Section 2 presents the Specifications. Section 3 presents Pilot and Non-Pilot applications with related Catalog Numbers for ordering purposes. MDAR Installation, Operation and Maintenance are described in Section 4, with related Setting Calculations in Section 5. Acceptance Tests for both Non-Pilot and Pilot System are described in Appendix H. Appendix I shows Index to Nomenclature. System Diagrams are included in Appendix J.

#### **Contents of Relay System**

The MDAR Relay System includes the style numbers, listed below, with appropriate sub numbers (representing revision levels) for each module. Addenda pages may be included (representing future revisions).

| Module                             | Style and Sub Number |

|------------------------------------|----------------------|

| Backplane                          | 1609C23-13           |

| (Sub-Backplane Xfmr)               | 1498B70-3            |

| <ul> <li>Interconnect</li> </ul>   | 1611C30-9            |

| Option                             | 1608C39-6            |

| Filter                             | 1608C38-9            |

| <ul> <li>Microprocessor</li> </ul> | 1611C14-7            |

| <ul> <li>Display</li> </ul>        | 1609C01-4            |

| Power Supply                       | 1608C35-16           |

#### Software System

MDAR software version V2.10 is included in this I.L.

#### **Setting Nomenclature Appliques**

If this I.L. is included as part of the shipment of an MDAR Relay system, the I.L. will contain setting nomenclature appliques which can be placed in a convenient location, e.g., inside the two FT-14 covers. The appliques provide a convenient (and complete) set of MDAR "settings" (see Table 4-1 for setting nomenclature). There are two appliques which are printed protective sheets (contained in a plastic envelope); the back of the sheets can be removed thereby exposing a stick-on surface.

### Features Included in Version V2.10

The following features are *standard* for the Non-Pilot MDAR V2.10:

- 3-Zone phase and ground distance relay, with reversible Zone 3 phase and ground; 4 impedance units per zone: 3 phase-to-ground; 1 phase-to-phase.

- Selectable Zone 1 extension

- Zone 1 timer (0 or 2 cycles)

- Independent timers for phase and ground (T2G, T2P, T3G, T3P)

- Inverse time directional or non-directional (selectable) ground overcurrent backup logic

- Loss of potential supervision (LOP)

- Loss of current monitoring (LOI)

- Overcurrent supervision of phase and ground distance

- Instantaneous forward directional phase and ground highset overcurrent trip (ITP and ITG)

- Close Into Fault Trip (CIFT)

- Stub Bus Protection (89b)

- Unequal-pole-closing load pickup logic

- Selectable Loss-of-Load accelerated trip logic

- Current change fault detector (ΔI)

- Voltage change fault detector ( $\Delta V$ )

- Line voltage, current and phase angle monitor.

- Last Fault LED blinks once for a single fault and twice for more than one fault. When the RESET button is depressed, the flashing LED is reset, and the displayed data is returned to the Volts/ Amps/Angle...metering mode. MDAR fault data memory cannot be cleared from the front panel. Fault data can be accessed by selecting Last Fault or Previous Fault Display Mode

- Selectable polarizing for directional O/C ground units (ZSEQ/NSEQ/DUAL)

- Programmable Reclose initiation and reclose block (RB) outputs; Reclose Initiate (RI2) can be enabled with the selection of:

- 1PR for  $\phi G$  fault

- 2PR for  $\phi G$  or  $\phi \phi$  fault

- 3PR for  $\phi G$  or  $\phi \phi$  fault or  $3\phi$  fault

- Numerical (Digital) Processing

- Fault locator

- Self-checking software with Failure Alarm and Displayed error codes

- · Push-to-close test for output contacts

- Software switches for functional tests, e.g., TK (SEND), RS1, RS2 and RS12 (Receivers).

- Trip contact sealed by trip current, with selectable dropout delay timer, 0/50 ms

- Real-time clock

- 16 fault record storage with selectable capture mode

- 16 sets of oscillographic data and intermediate target data. Each set includes 7 analog graphic inputs and 24 digital intermediate targets with 8 samples per cycle. Each analog input contains 1 prefault and 7 fault cycles

- Selectable oscillographic data capture setting trip, Z2PU, Z2Z3 or  $\Delta V / \Delta I$

- Selectable Data Capture Setting (FDAT) TRIP, Z2PU/TRIP, Z2Z3/TRIP

- Logic for load restrictions

- Selectable phase sequence rotation of ABC or ACB

- Out-of-Step block logic

NOTE: The foregoing (and following) features preceded by two dots (••) were not included in V2.02.

#### Features Included in Version V2.10

The following features are *standard* for the Pilot MDAR V2.10:

- All features listed as standard for the Non-Pilot MDAR V2.10 are included in the Pilot system

- Independent pilot phase and ground distance units

- Complete Logic and Channel Interface for:

- Permissive Overreach Transfer Trip (POTT) / Simplified Unblocking

- Permissive Underreach Transfer Trip (PUTT)

- Directional Comparison Blocking Scheme (BLK)

- POTT or Simplified Unblocking Weakfeed

- Instantaneous Forward Directional Overcurrent Function for High Resistance Ground Fault Supplement to Overreach Pilot, with adjustable timer (from 0 to 15) in 1 cycle steps or Block

- Instantaneous Reverse Directional Overcurrent Ground Function

- Carrier Ground Start on Blocking Scheme

- Weakfeed System Application

- Reclose Block on Breaker Failure (BF) Squelch

- 3-Terminal Line Application

- Weakfeed Trip

#### Features Included in Version V2.10

The following features are *optional* for the Non-Pilot *and* the Pilot MDAR V2.10:

| Choice of rear communications port options:                                               | TTYP       | SET | AT TRIP                          | <u>RI</u>        |                       |

|-------------------------------------------------------------------------------------------|------------|-----|----------------------------------|------------------|-----------------------|

| RS232C/PONI or                                                                            | OFF        |     | 3PT                              | NO               |                       |

| INCOM <sup>®</sup> /PONI                                                                  | 1PR        |     | 3PT                              | RI2              | ( <b></b> \$G)        |

| Optional graphic software program (OSCAR)                                                 | 2PR<br>3PR |     | 3PT<br>3PT                       | RI2<br>RI2       | (φG, φφG)<br>(φG, Mφ) |

| <ul> <li>Built-in FT-14 test switches</li> </ul>                                          | SPR        |     | SPT (¢G)                         | RI1              |                       |

| Optional Programmable Output Contacts. Eight additional contacts chosen from 30 functions | SR3R       |     | 3ΡΤ (Μφ)<br>SPT (φG)<br>3ΡΤ (Μφ) | N0<br>RI1<br>RI2 |                       |

| <ul> <li>Single-Pole-Trip (SPT) logic and outputs:</li> </ul>                             |            |     | 51 Τ (Μφ)                        | 1112             |                       |

| <ul> <li>SPT/RI1 on first</li></ul>                                                       | SPT        | =   | Single Pole Trip                 |                  |                       |

| types                                                                                     | 3PT        | =   | 3 Pole Trip                      |                  |                       |

| <ul> <li>3PT/RB if reclosing on a permanent fault</li> </ul>                              | RI         | =   | Reclose Initiate                 |                  |                       |

| <ul> <li>3PT/RB if second phase(s) fault during single</li> </ul>                         | RB         | =   | Reclose Block                    |                  |                       |

| phasing                                                                                   | RI2        | =   | 3 Pole Reclose Initiate          |                  |                       |

| <ul> <li>3PT on a time delay limit (0.35-5.0 sec in 0.05</li> </ul>                       | RI1        | =   | Single Pole Reclose Ir           | itiate           |                       |

| sec steps) if the system fails to reclose (62T).                                          | φG         | =   | Single Phase-to-Grour            | nd Faul          | ts                    |

| Setting options for TRIP/Reclose Initiate (RI)                                            | Μφ         | =   | Multi-Phase Faults               |                  |                       |

| mode selector:                                                                            | φφ         | =   | 2-Phase Faults                   |                  |                       |

#### NOTE: The foregoing (and following) features preceded by two dots (••) were not included in V2.02.

#### Significant Changes to V2.10 (from V2.02)

(For customers who are familiar with Version 2.00 and beyond)

- 1. Add an O/C supervision (Im) for Phase faults (AND-2, AND-4, AND-6 & AND-191) and OST (AND-131C & AND-122). Remove IL supervision from AND-131C & AND-122).

- 2. Change PT setting range from 300-7000 to 100-7000 with 5 per steps.

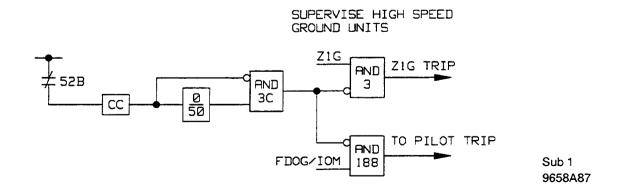

- 3. Modify 52b control circuit by adding an AND-3C to supervise Z1G (AND-3A) and FDOG (AND-188) trip. For V2.02, the ground units will not trip if the breaker is open, e.g., 52b = 125 volts.

- 4. Modify SPT logic by adding OR75B and changing the input of OR78J from X2 to X2A (0/50). For version 2.02, the MDAR relay will not trip after single pole reclosing on a permanent SPF if the setting of LV is very low because the LV setting supervises the ROF tripping.

- 5. Add eight programmable contact outputs with two programmable timers which can be set for pickup and dropout from 0 to 5 seconds with 0.01 sec per steps.

- 6. Selectable ABC or ACB phase rotation by jumper #3. The rotation is shown on the Metering mode.

#### NOTE: For rotation ABC, jumper #3 on the Microprocessor Module should be removed.

- 7. Change the input of AND-120 from the switch of PLT to BLK. The STOP contact should be operated only for the Blocking system.

- 8. Add a display saver routine. The MDAR display will be on for 5 minutes after turning the dc power on, depressing any one of the front panel pushbuttons or detecting faults on the line.

- 9. Change front target display from "IN" to "IP" and add two readings " $3I_0$ " and " $\angle 3I_0$ " to the fault target display.

# NOTE: CONVERSION FROM MDAR FIRMWARE VERSION V2.0x TO V2.10 CAN BE ACCOMPLISHED AS FOLLOWS:

- 1. Standard precautions of static voltage discharges should be observed such as using a grounded wrist strap when handling Integrated Circuits.

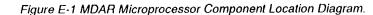

- 2. Remove chips U103, U104, and U202 from the Microprocessor module.

- 3. Replace chips U103 (G11) and U104 (G12) and U202 into the sockets.

- 4. Check Jumper #3 on Microprocessor module for rotation ABC or ACB system which is shown on the Metering mode. Normally, JMP3 should be "OUT" for ABC system. Spare jumpers should be placed on locations JMP10, 11 or 12. Remove any spare jumper (JMP10, 11 or 12) and replace it to JMP3 position for ACB system.

- 5. Check Jumper #2 on Microprocessor module. Position 2-3 is used for single-pole trip logic only and position 1-2 is used for three-pole trip or programmable output contact logic.

- 6. Reprogram MDAR password through INCOM<sup>®</sup> remote communication.

- 7. It is recommended to verify the relay's operation per Section 2 of Appendix H (Acceptance/Maintenance Tests).

# TABLE OF CONTENTS

# Section 1. PRODUCT DESCRIPTION

| 1.1 | INTRODUCTION                                       |

|-----|----------------------------------------------------|

| 1.2 | MDAR CONSTRUCTION 1-1                              |

| 1.3 | MDAR MODULES                                       |

| 1.4 | TEST ACCESSORIES 1-3                               |

| 1.5 | FAULT DETECTION SOFTWARE 1-3                       |

| 1.6 | SELF-CHECKING SOFTWARE 1-4                         |

| 1.7 | UNIQUE REMOTE COMMUNICATION (WRELCOM®) PROGRAM 1-5 |

| 1.8 | POWER SYSTEM ROTATION ABC OR ACB SELECTION         |

# Section 2. SPECIFICATIONS

| TECHNICAL                                                                            |

|--------------------------------------------------------------------------------------|

| EXTERNAL CONNECTIONS 2-2                                                             |

| CONTACT DATA                                                                         |

| MEASUREMENTS 2-2                                                                     |

| MEASUREMENT UNITS 2-2                                                                |

| SETTING RANGES 2-2                                                                   |

| GROUND/ PHASE OVERCURRENTS AND UNDERVOLTAGE UNITS 2-2                                |

| OPTIONAL SINGLE-POLE-TRIP LOGIC AND OUTPUTS<br>(Without Programmable Contact Option) |

| OPTIONAL PROGRAMMABLE OUTPUT CONTACTS<br>(Without Single-pole Trip Option) 2-3       |

| OUT-OF-STEP BLOCK                                                                    |

| SELECTABLE PHASE SEQUENCE ABC OR ACB ROTATION                                        |

| OPTIONAL COMMUNICATION INTERFACE                                                     |

| CHASSIS DIMENSIONS AND WEIGHT 2-3                                                    |

| ENVIRONMENTAL DATA 2-3                                                               |

|                                                                                      |

# Section 3. APPLICATIONS AND ORDERING INFORMATION

| 3.   | NON-PILOT SYSTEM                                                                                                         |

|------|--------------------------------------------------------------------------------------------------------------------------|

| 3.1  | LINE MEASUREMENT TECHNIQUES                                                                                              |

| 3.2  | MEASUREMENT ZONES 3-2                                                                                                    |

| 3.3  | MDAR NON-PILOT FEATURES 3-4                                                                                              |

| 3.4  | PILOT SYSTEM                                                                                                             |

| 3.5  | 3-ZONE DISTANCE PHASE AND GROUND WITH INDEPENDENT<br>PILOT PHASE AND GROUND 3-14                                         |

| 3.6  | INVERSE TIME DIRECTIONAL OR NON-DIRECTIONAL<br>(SELECTABLE) OVERCURRENT GROUND BACKUP                                    |

| 3.7  | INSTANTANEOUS REVERSE DIRECTIONAL<br>OVERCURRENT GROUND FUNCTION                                                         |

| 3.8  | LOSS-OF-POTENTIAL SUPERVISION)                                                                                           |

| 3.9  | LOSS-OF-CURRENT MONITORING                                                                                               |

| 3.10 | OVERCURRENT SUPERVISION 3-15                                                                                             |

| 3.11 | INSTANTANEOUS OVERCURRENT TRIP                                                                                           |

| 3.12 | HIGH-SET INSTANTANEOUS DIRECT TRIP,<br>INCLUDING THREE-PHASE AND ONE GROUND<br>OVERCURRENT UNITS FOR SPT/3PT APPLICATION |

| 3.13 | CLOSE-INTO-FAULT TRIP AND STUB BUS PROTECTION                                                                            |

| 3.14 | UNEQUAL-POLE CLOSING LOAD PICKUP LOGIC)                                                                                  |

| 3.15 | SELECTABLE LOSS-OF-LOAD ACCELERATED TRIP LOGIC                                                                           |

| 3.16 | CURRENT CHANGE FAULT DETECTOR 3-15                                                                                       |

| 3.17 | VOLTAGE CHANGE FAULT DETECTOR                                                                                            |

| 3.18 | 3-TERMINAL LINE APPLICATION                                                                                              |

| 3.19 | WEAKFEED TRIP APPLICATION                                                                                                |

| 3.20 | LOGIC FOR RB ON BF SQUELCH 3-16                                                                                          |

| 3.21 | OUT-OF-STEP (OS) LOGIC                                                                                                   |

| 3.22 | OPTIONAL SINGLE-POLE TRIP (SPT) LOGIC AND OUTPUTS (<br>Without Programmable Output Contact Option                        |

| 3.23 | OPTIONAL PROGRAMMABLE OUTPUT CONTACTS<br>WITHOUT SPT OPTION                                                              |

| 3.24 | MDAR Ordering Information                                                                                                |

## Section 4. INSTALLATION, OPERATION AND MAINTENANCE

| 4.   | SEPARATING THE INNER AND OUTERCHASSIS           |

|------|-------------------------------------------------|

| 4.1  | TEST PLUGS AND FT-14 SWITCHES4-1                |

| 4.2  | EXTERNAL WIRING 4-1                             |

| 4.3  | MDAR FRONT PANEL DISPLAY 4-2                    |

| 4.4  | FRONT PANEL OPERATION                           |

| 4.5  | JUMPER CONTROLS 4-5                             |

| 4.6  | COMMUNICATION INTERFACE 4-5                     |

| 4.7  | SIXTEEN FAULT TARGET DATA 4-6                   |

| 4.8  | OSCILLOGRAPHIC DATA (Standard)4-6               |

| 4.9  | PROGRAMMABLE CONTACT OUTPUTS (Optional Feature) |

| 4.10 | ROUTINE VISUAL INSPECTION 4-6                   |

| 4.11 | ACCEPTANCE TESTING 4-6                          |

| 4.12 | NORMAL PRECAUTIONS 4-7                          |

| 4.13 | DISASSEMBLY PROCEDURES 4-7                      |

# Section 5. SETTING CALCULATIONS

|       | 5.     | CALCULATION OF MDAR SETTINGS                       |

|-------|--------|----------------------------------------------------|

|       | 5.1    | SELECTION OF MDAR SETTINGS 5-5                     |

|       | 5.2    | GUIDANCE FOR RECLOSING INITIATION MODE PROGRAMMING |

|       | 5.3    | SELECTION OF PROGRAMMABLE CONTACTS                 |

| Apper | ndix A | BACKPLANE MODULE A-1                               |

| Apper | ndix B | INTERCONNECT MODULEB-1                             |

| Apper | ndix C | COPTION MODULE                                     |

| Apper | ndix D | . FILTER MODULED-1                                 |

| Apper | ndix E | . MICROPROCESSOR MODULEE-1                         |

| Appendix F  | DISPLAY MODULE F-1                             |

|-------------|------------------------------------------------|

| Appendix G  | 6. POWER SUPPLY MODULE G-1                     |

| Appendix H  | I-1. FULL PERFORMANCE TESTS (V2.10) H-1        |

| 1.          | FULL PERFORMANCE TESTS                         |

| 1.1.        | NON-PILOT PERFORMANCE TESTS                    |

| 1.2.        | PILOT PERFORMANCE TESTS                        |

| 1.3.        | SINGLE POLE TRIP (OPTION) ACCEPTANCE TESTS     |

| 1.4.        | MDAR WITH OUT-OF-STEP BLOCK OPTION             |

|             |                                                |

| Appendix H  | I-2. ACCEPTANCE/MAINTENANCE TESTS (V2.10) H-13 |

| 2.          | MAINTENANCE QUALIFICATION TESTS                |

| 2.1.        | NON-PILOT MAINTENANCE TESTS                    |

| 2.2.        | PILOT MAINTENANCE TEST                         |

| 2.3.        | SINGLE-POLE TRIP TEST                          |

|             |                                                |

| Appendix I. | Index/Glossary of NomanclatureINDEX-1          |

| Appendix J  | . System DiagramsJ-1                           |

### Trademarks

All terms mentioned in this book that are known to be trademarks or service marks are listed below. In addition, terms suspected of being trademarks or service marks have been appropriately capitalized. ABB Power T&D Company Inc. cannot attest to the accuracy of this information. Use of a term in this book should not be regarded as affecting the validity of any trademark or service mark.

IBM and PC are registered trademarks of the International Business Machines Corporation. WRELCOM is the registered trademark of the ABB Power T&D Company Inc. INCOM is the registered trademark of the Westinghouse Electric Corporation

# FIGURES

### FIGURE NO.

#### PAGE

| 1-1   | MDAR Relay Assembly (without FT-14 Switches)                          |

|-------|-----------------------------------------------------------------------|

| 1-2   | Layout of MDAR Modules within Inner and Outer Chassis                 |

| 1-3   | INCOM/PONI Communication Interface Device (photo)                     |

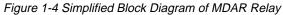

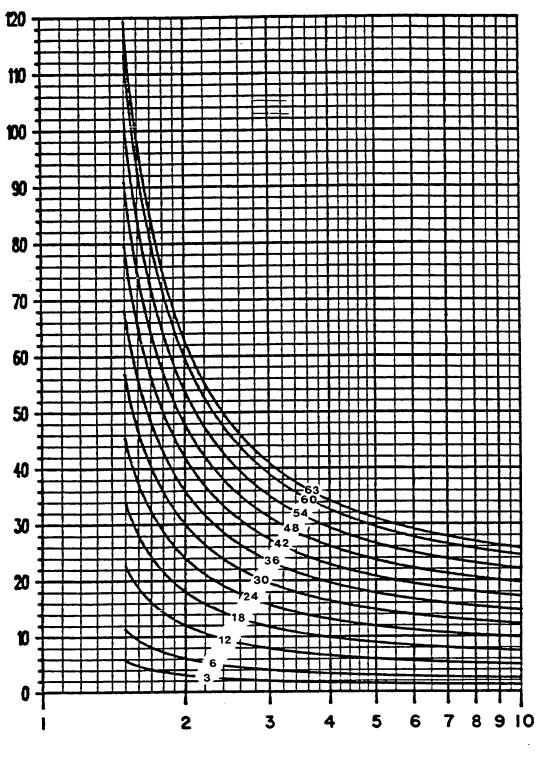

| 1-4   | Simplified Block Diagram of MDAR Relay                                |

| 1-5   | MDAR Relay Program Functions                                          |

| 2-1   | CO-2 Curve Characteristics                                            |

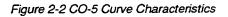

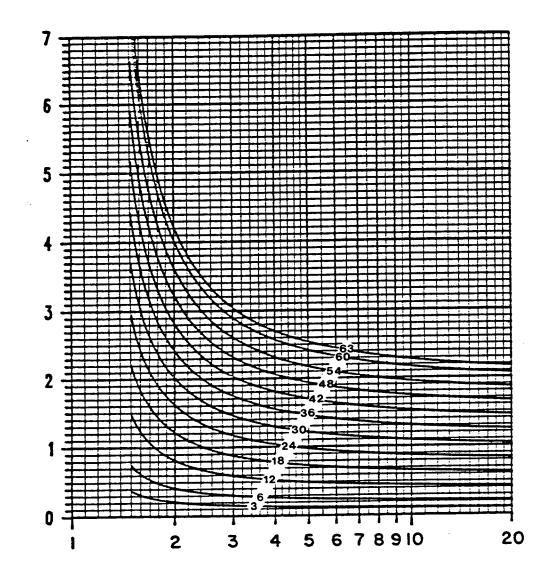

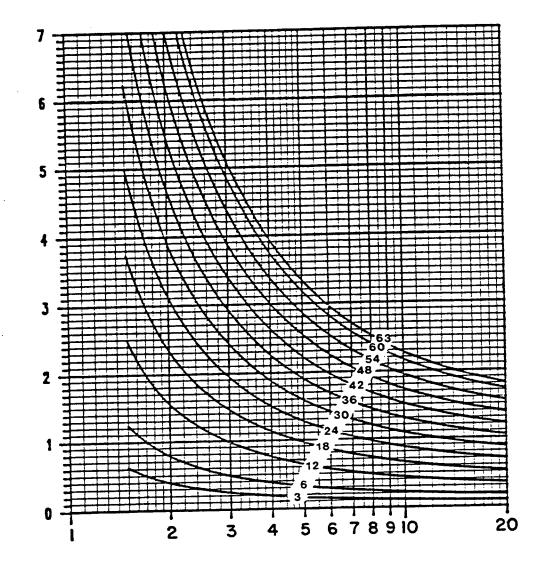

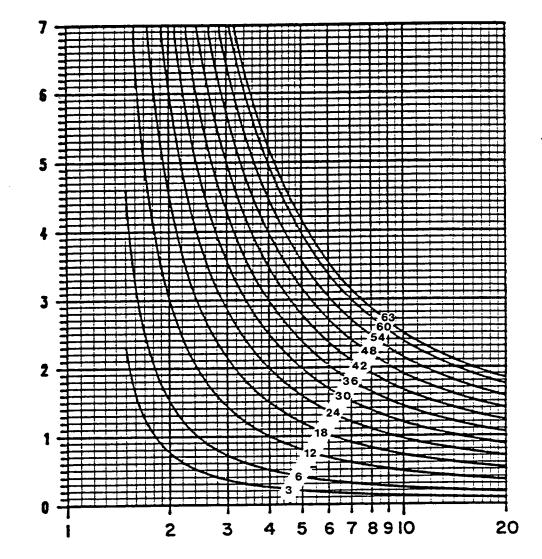

| 2-2   | CO-5 Curve Characteristics                                            |

| 2-3   | CO-6 Curve Characteristics                                            |

| 2-4   | CO-7 Curve Characteristics                                            |

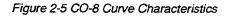

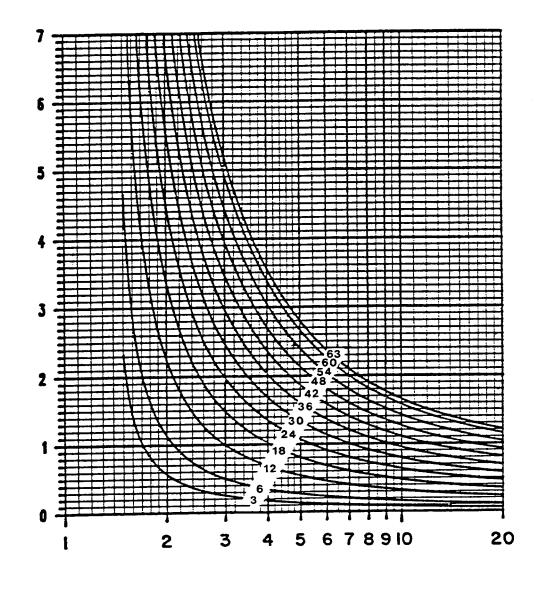

| 2-5   | CO-8 Curve Characteristics                                            |

| 2-6   | CO-9 Curve Characteristics                                            |

| 2-7   | CO-11Curve Characteristics                                            |

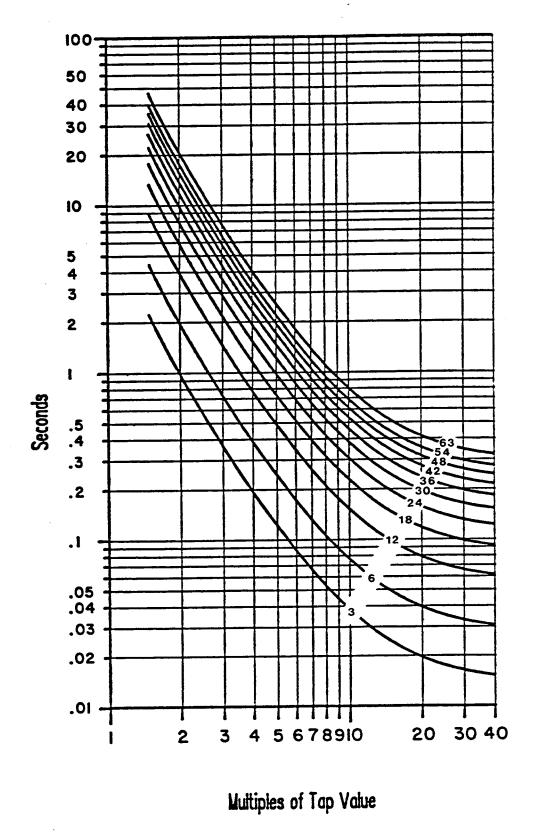

| 2-8   | MDAR Outline Drawing                                                  |

| 2-9   | MDAR Backplane Drawing (Rear View)                                    |

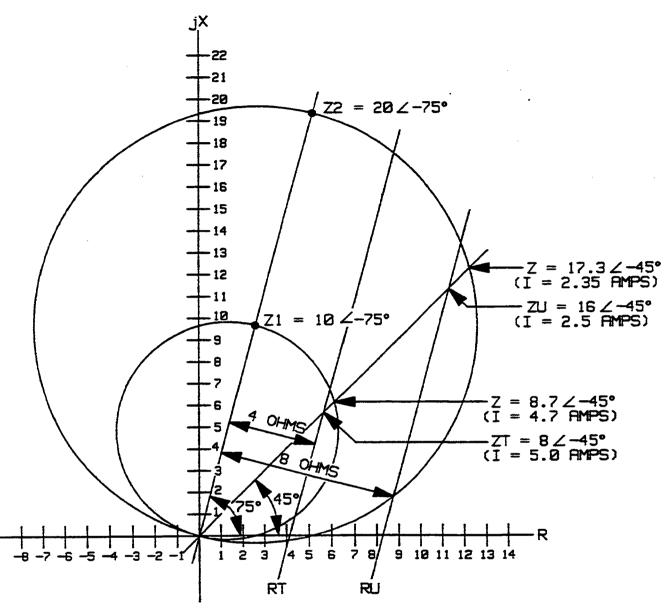

| 3-1   | MDAR Characteristics/R-X Diagram                                      |

| 3-2   | Mho Characteristic for Phase-to-Ground Faults                         |

| 3-3   | Mho Characteristics for Three-Phase Faults (No Load Flow)             |

| 3-4   | Mho Characteristics for Phase-to-Phase and Two-Phase-to-Ground        |

|       | Faults (No Load Flow)                                                 |

| 3-5   | MDAR Zone-1 Trip Logic                                                |

| 3-6   | MDAR Zone-2 Trip Logic                                                |

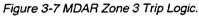

| 3-7   | MDAR Zone-3 Trip Logic                                                |

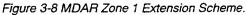

| 3-8   | MDAR Zone-1 Extension Scheme                                          |

| 3-9   | Inverse Time Overcurrent Ground Backup Logic                          |

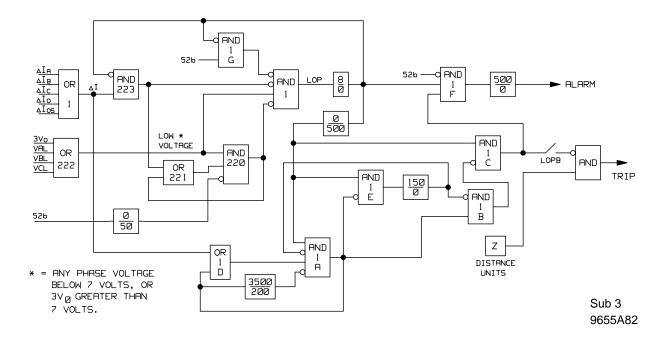

| 3-10  | Loss of Potential Logic.                                              |

| 3-11  | Loss of Potential Logic (System Diagram)                              |

| 3-12  | AC Current Monitoring Logic                                           |

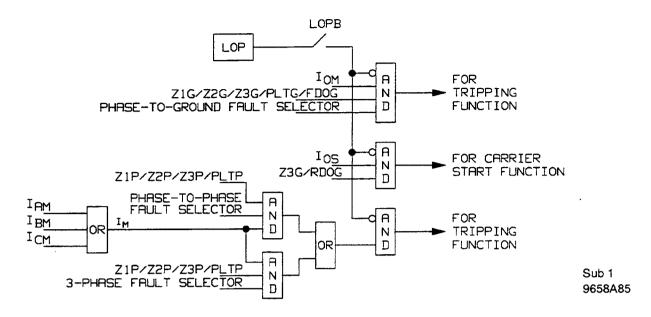

| 3-13  | Overcurrent Supervision                                               |

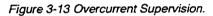

| 3-14  | Instantaneous Overcurrent Highset Trip Logic                          |

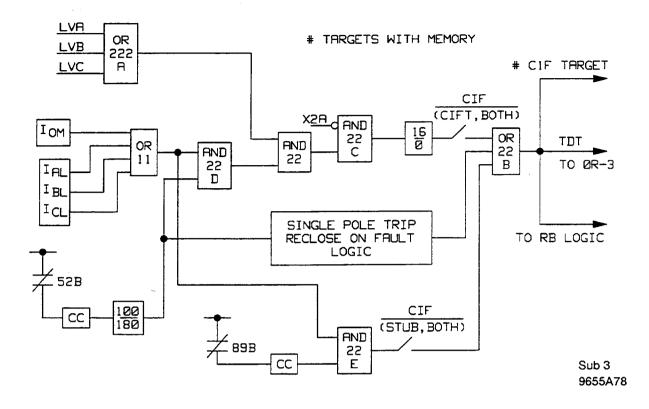

| 3-15  | MDAR Close-Into-Fault Trip (CIFT) Logic and Stub Bus Protection Logic |

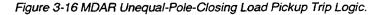

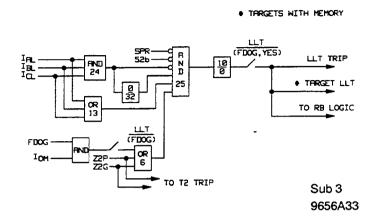

| 3-16  | MDAR Unequal-Pole-Closing Load Pickup Trip Logic                      |

| 3-17  | Load Loss Accelerated Trip Logic                                      |

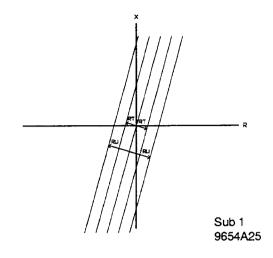

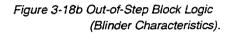

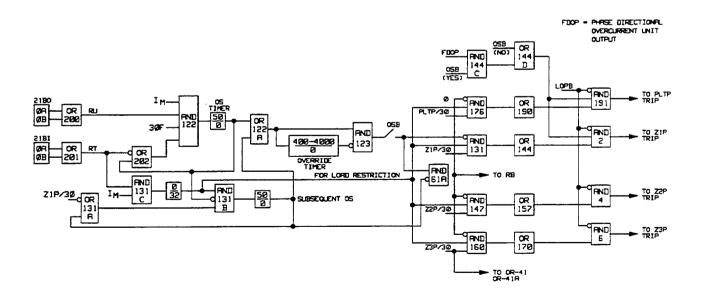

| 3-18a | Out-of-Step Block Logic                                               |

| 3-18b | Out-of-Step Block Logic (Blinder Characteristics)                     |

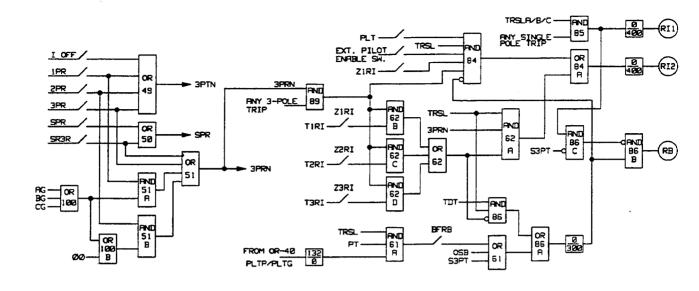

| 3-19  | Reclosing Initiation Logic                                            |

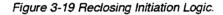

| 3-20  | Single Pole Trip Logic                                                |

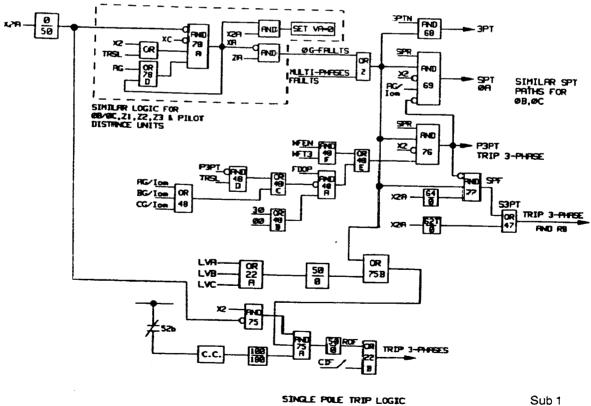

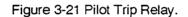

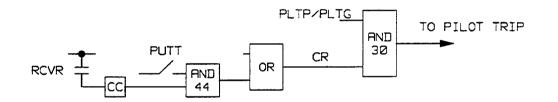

| 3-21  | Pilot Trip Relay.                                                     |

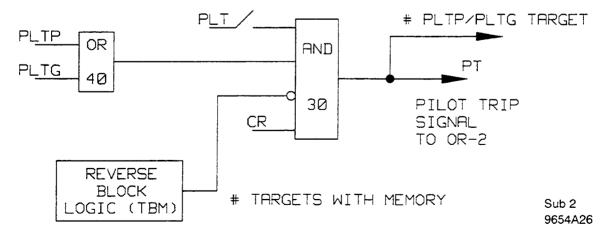

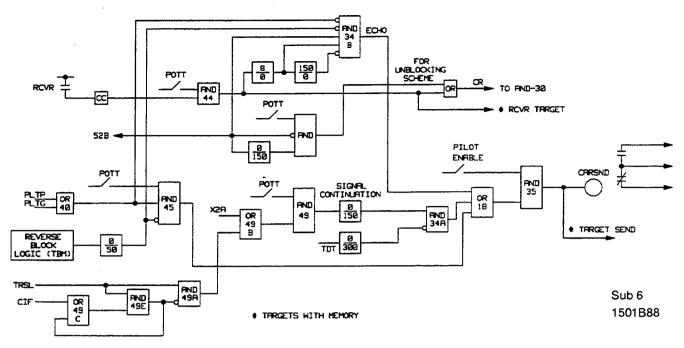

| 3-22  | POTT/Unblocking Pilot Trip Logic                                      |

| 3-23  | Carrier Keying/Receiving Logic in POTT/Unblocking schemes             |

FIGURE NO.

#### PAGE

|   | 3-24 | PUTT Keying Logic                                                               |

|---|------|---------------------------------------------------------------------------------|

|   | 3-25 | Blocking System Logic                                                           |

|   | 3-26 | PLTG supplemented by FDOG                                                       |

| - | 3-27 | Power Reversed on POTT/Unblocking Schemes                                       |

|   | 3-28 | Unequal Pole Closing on Fault                                                   |

|   | 3-29 | Additional Logic for POTT/Unblocking Schemes on 3-Terminal                      |

|   |      | Line Application                                                                |

|   | 3-30 | Additional Logic for PUTT Scheme on 3-Terminal                                  |

|   |      | Line Application                                                                |

|   | 3-31 | Weakfeed Application                                                            |

| I | 3-32 | Reversible Zone 3 Phase and Ground (Reverse Block Logic)                        |

|   | 3-33 | Composite Signal for Programmable Output Contacts                               |

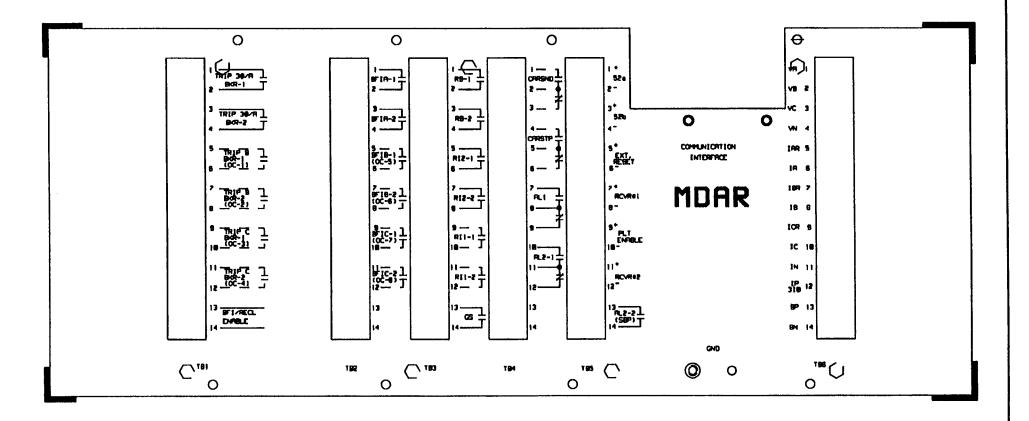

|   | 4-1  | MDAR Backplate                                                                  |

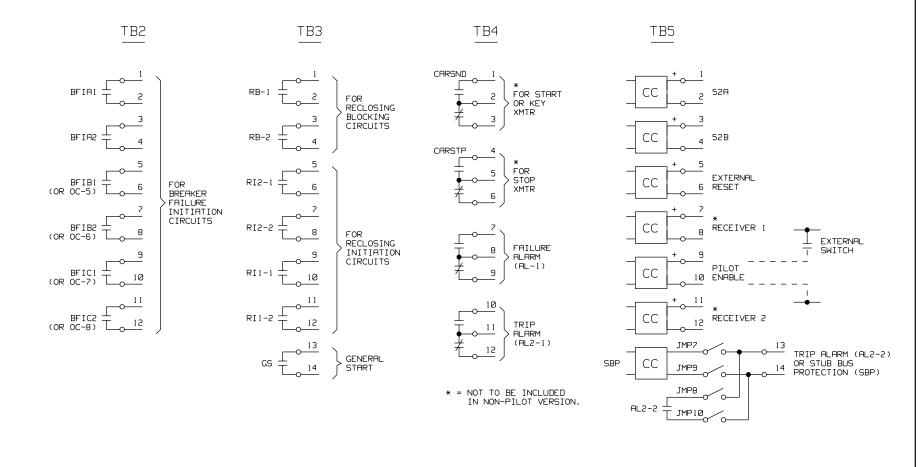

|   | 4-2  | MDAR Backplane PC Board Terminals                                               |

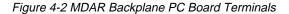

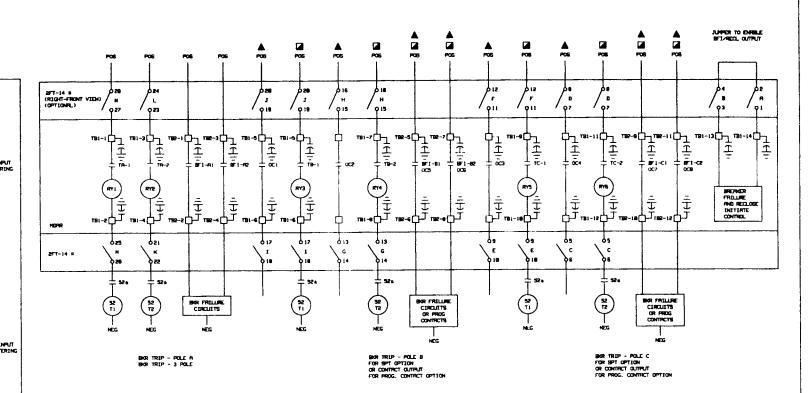

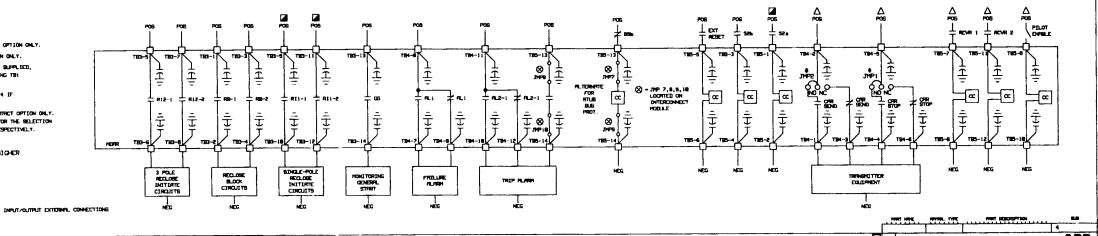

|   | 4-3  | MDAR System External Connection                                                 |

|   | A-1  | MDAR Backplane Module PC Board                                                  |

|   | A-2  | MDAR Backplane/Transformer Module PC Board                                      |

|   | A-3  | MDAR Backplane/Transformer Module Schematic                                     |

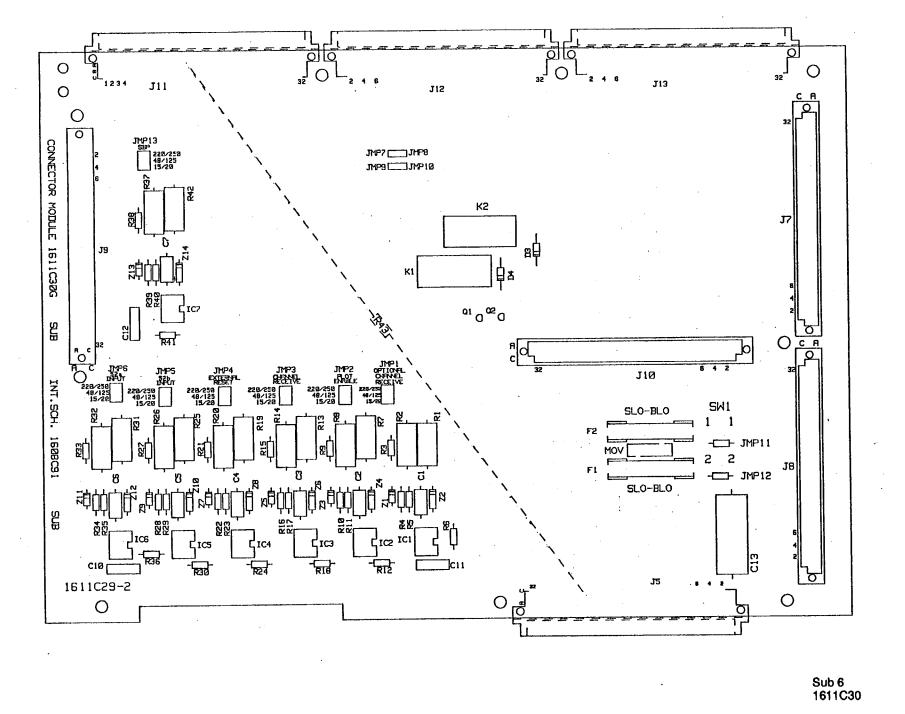

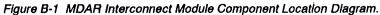

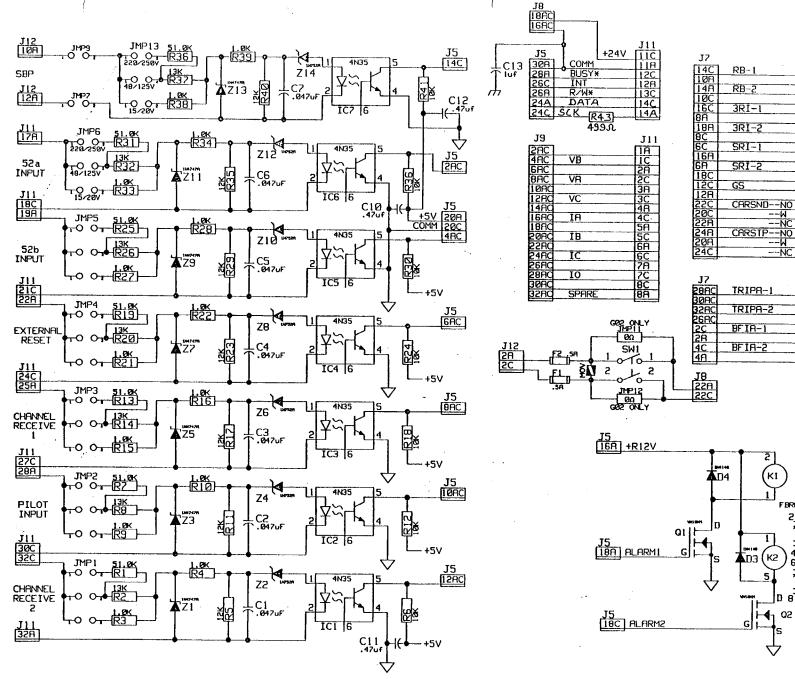

|   | B-1  | MDAR Interconnect Module PC Board                                               |

|   | B-2  | MDAR Interconnect Module Schematic                                              |

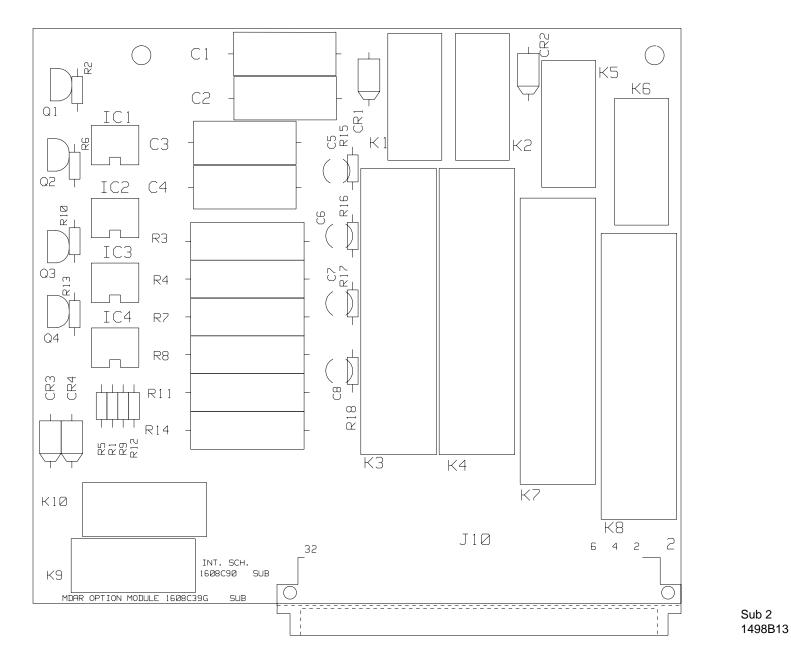

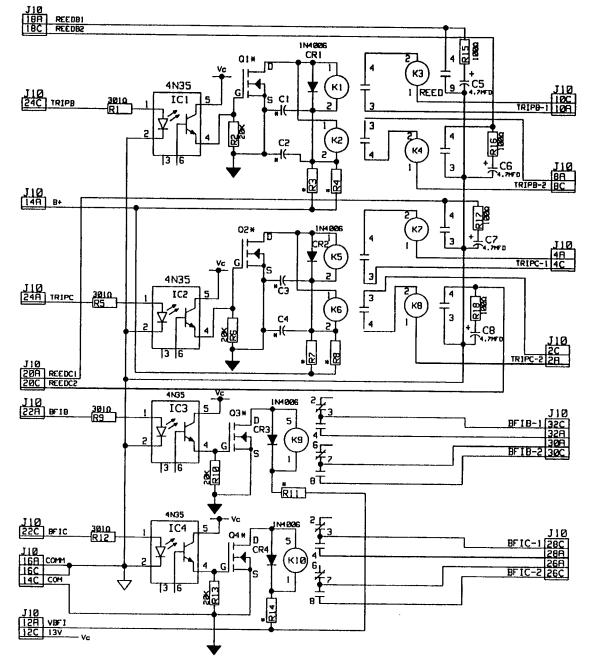

|   | C-1  | MDAR Option Module PC Board                                                     |

|   | C-2  | MDAR Option Module Schematic                                                    |

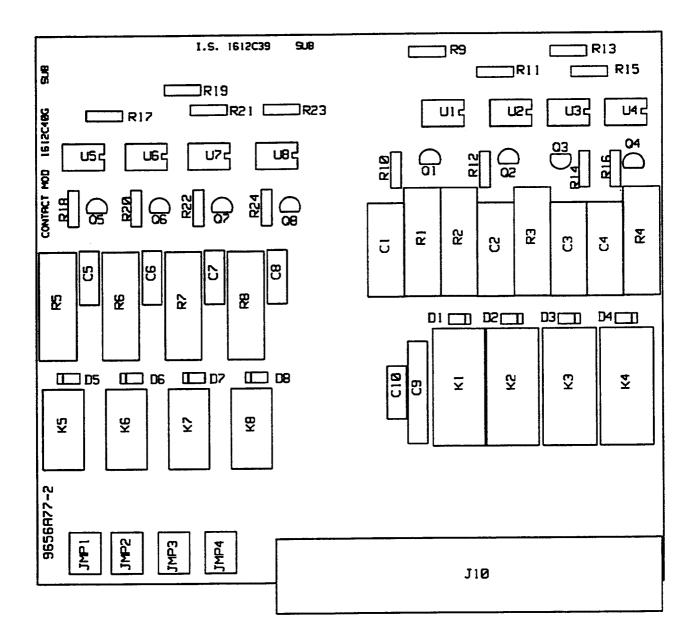

|   | C-3  | MDAR Contact Module PC Board                                                    |

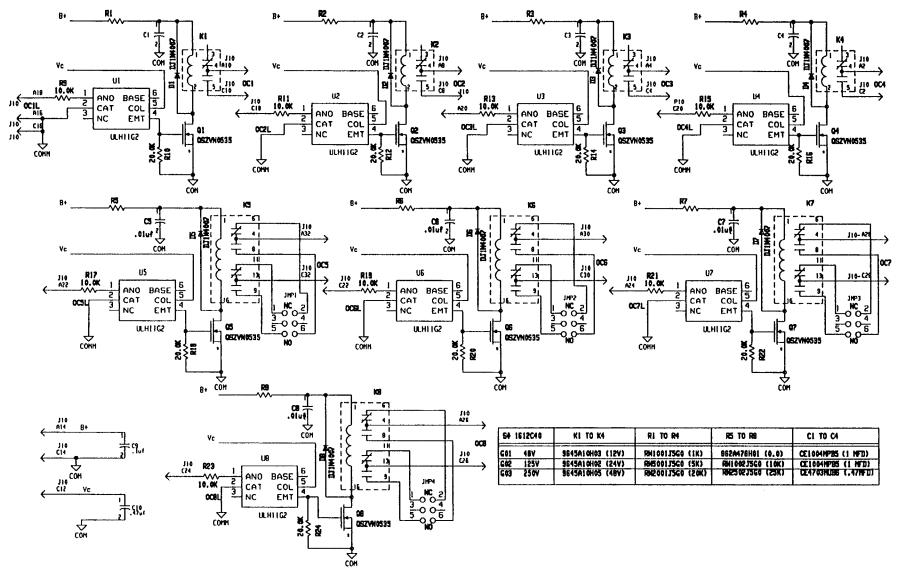

|   | C-4  | MDAR Contact Module Schematic                                                   |

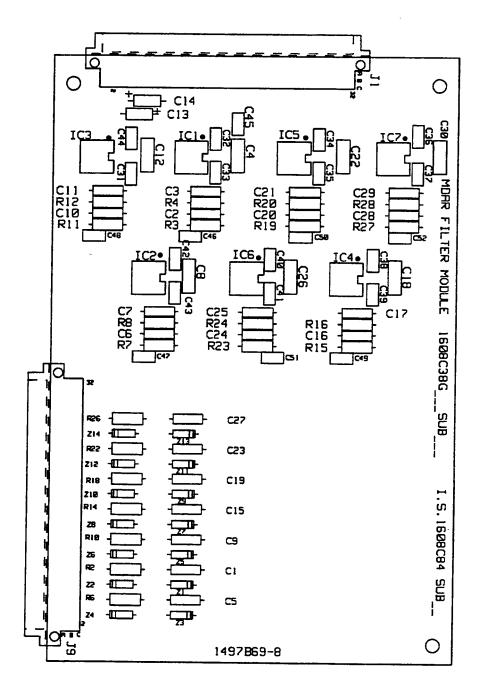

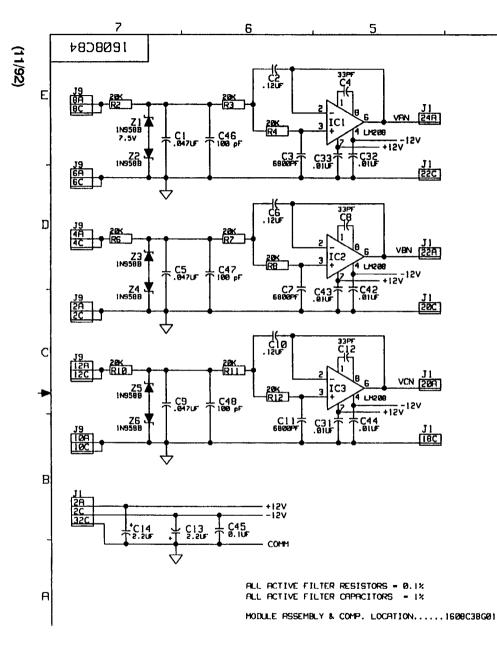

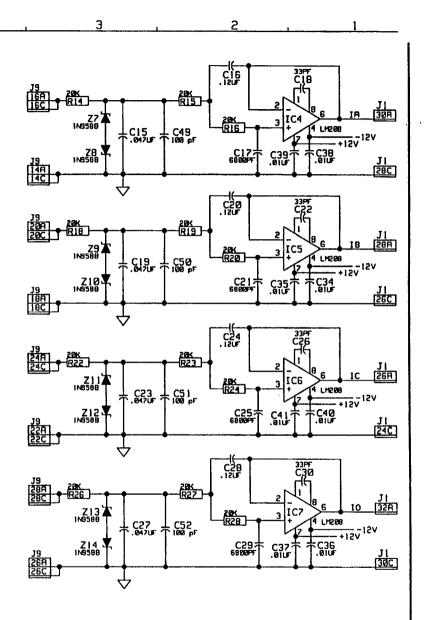

|   | D-1  | MDAR Filter Module PC Board                                                     |

|   | D-2  | MDAR Filter Module Schematic                                                    |

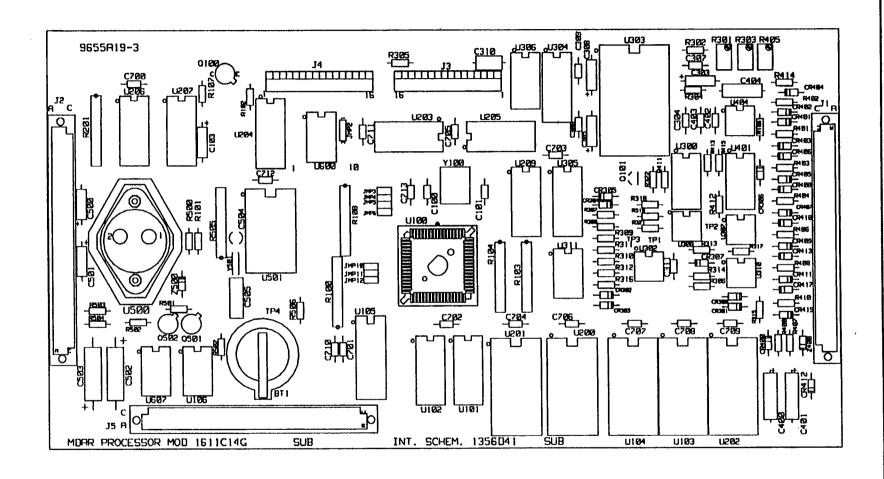

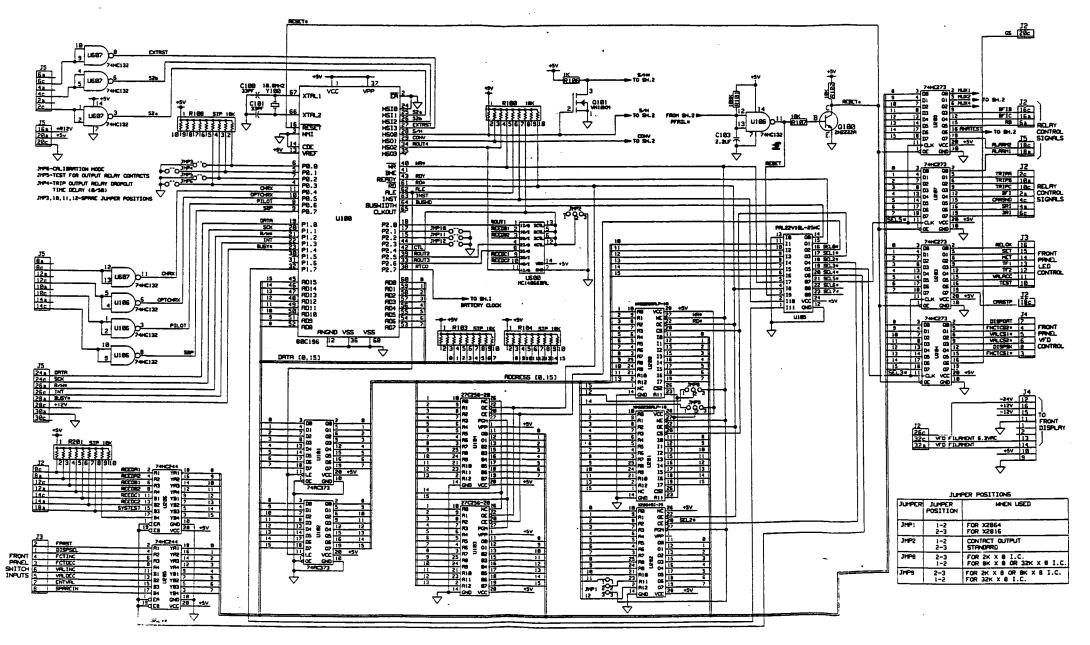

|   | E-1  | MDAR Microprocessor Module PC Board                                             |

|   | E-2  | MDAR Microprocessor Module Schematic (sheet 1 of 2)                             |

|   | E-3  | MDAR Microprocessor Module Schematic (sheet 2 of 2)                             |

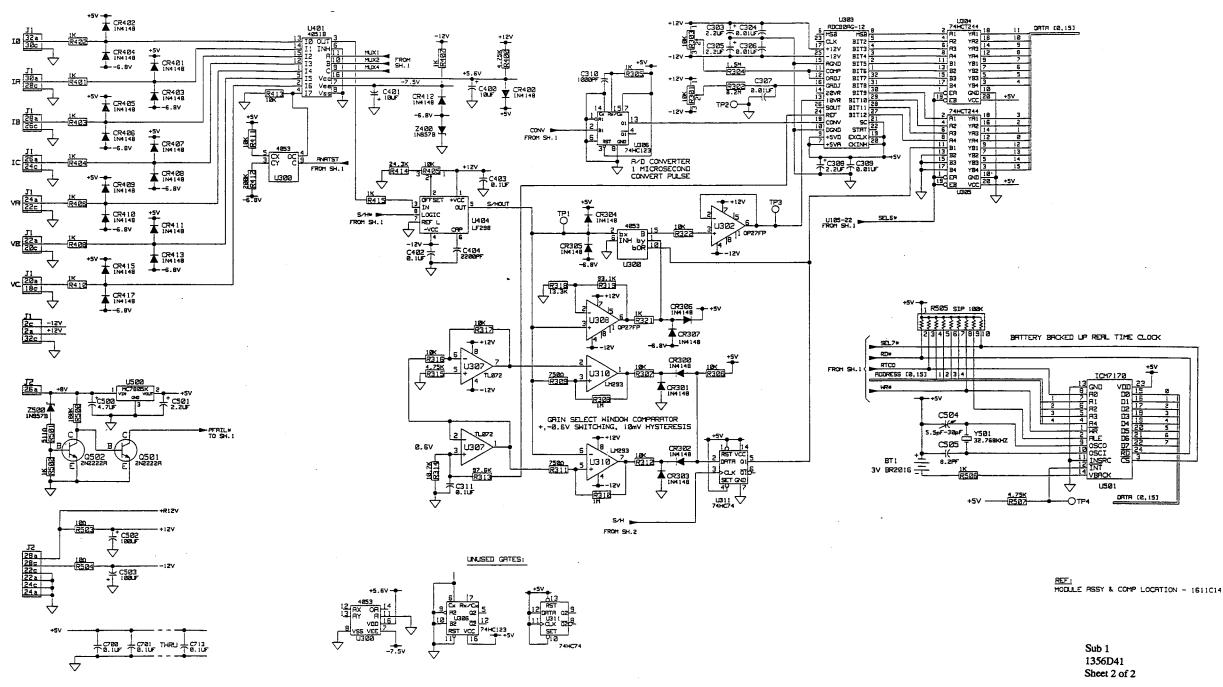

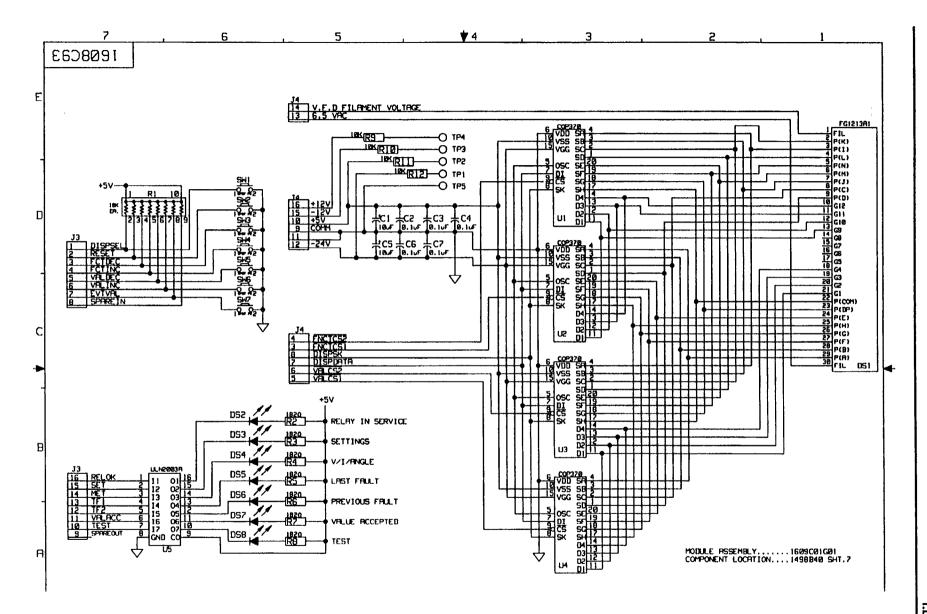

|   | F-1  | MDAR Display Module PC Board                                                    |

|   | F-2  | MDAR Display Module Schematic                                                   |

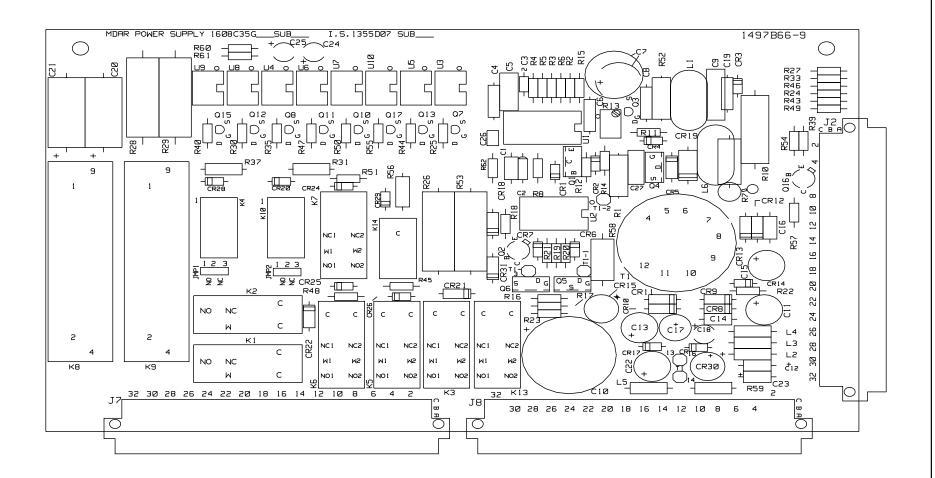

|   | G-1  | MDAR Power Supply PC Board                                                      |

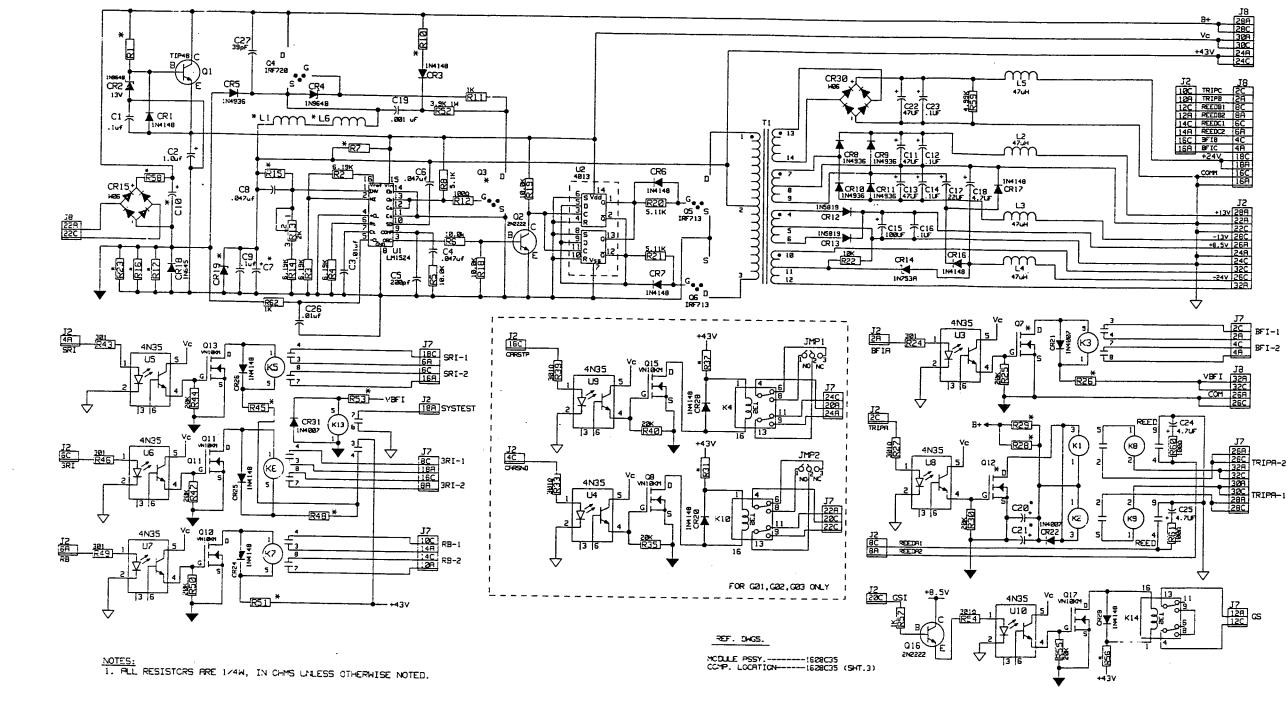

|   | G-2  | MDAR Power Supply Schematic                                                     |

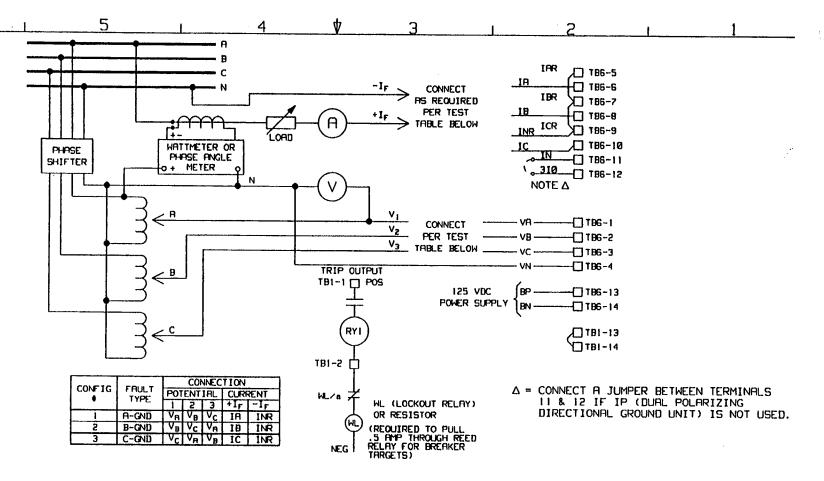

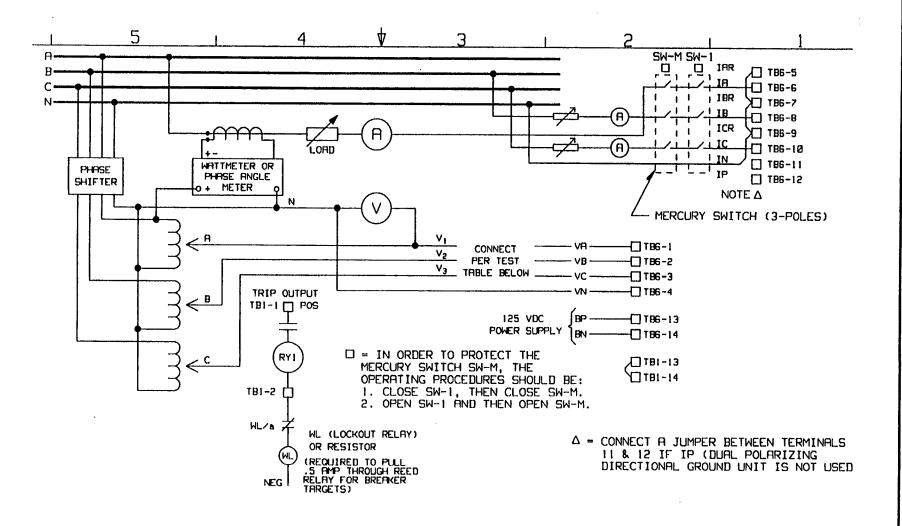

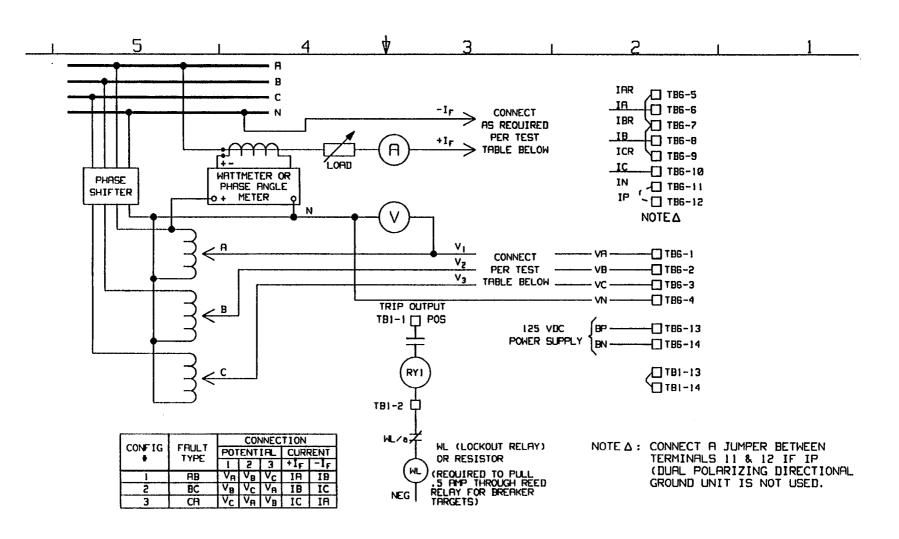

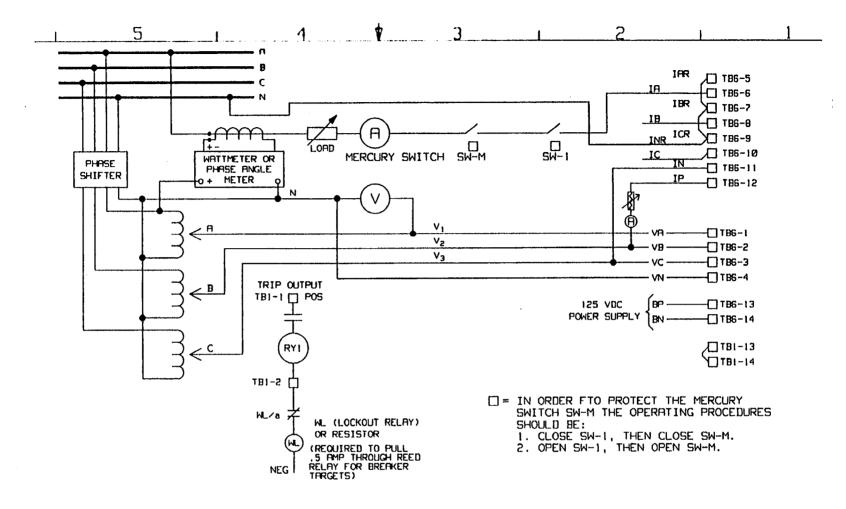

|   | H-1  | Test Connection for Single-Phase-to-Ground Faults (sheet 1 of 4)                |

|   | H-2  | Test Connection for Three-Phase Faults (sheet 2 of 4)                           |

|   | H-3  | Test Connection for Phase-to-Phase Faults (sheet 3 of 4)                        |

|   | H-4  | Test Connection for Dual Polarizing Ground Directional Unit (sheet 4 of 4) H-19 |

|   | H-5  | MDAR with Out-of-Step Block Option                                              |

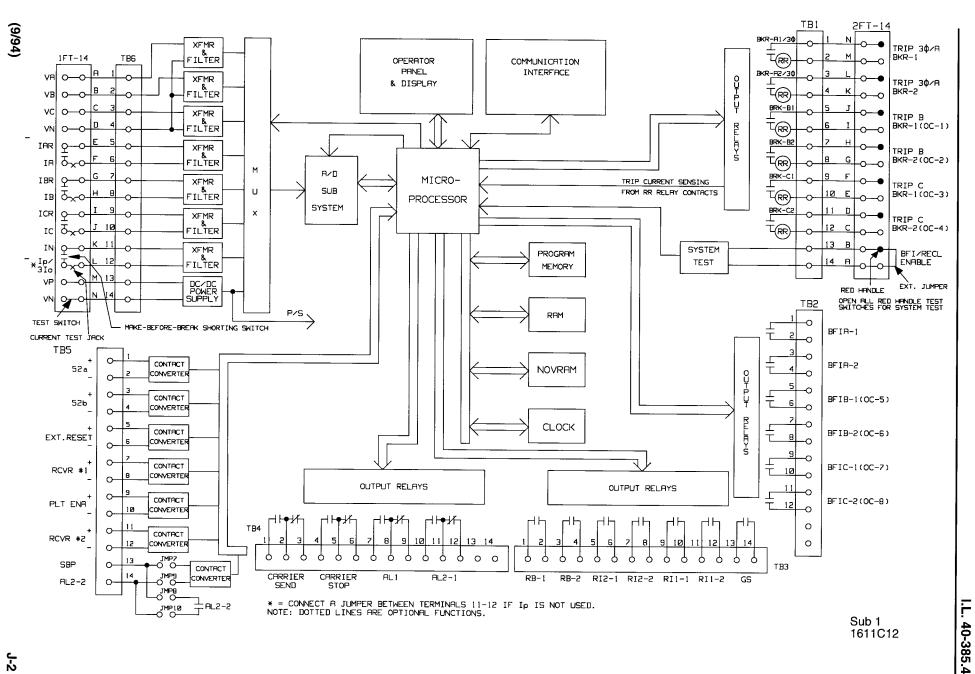

|   | J-1  | MDAR Block Diagram                                                              |

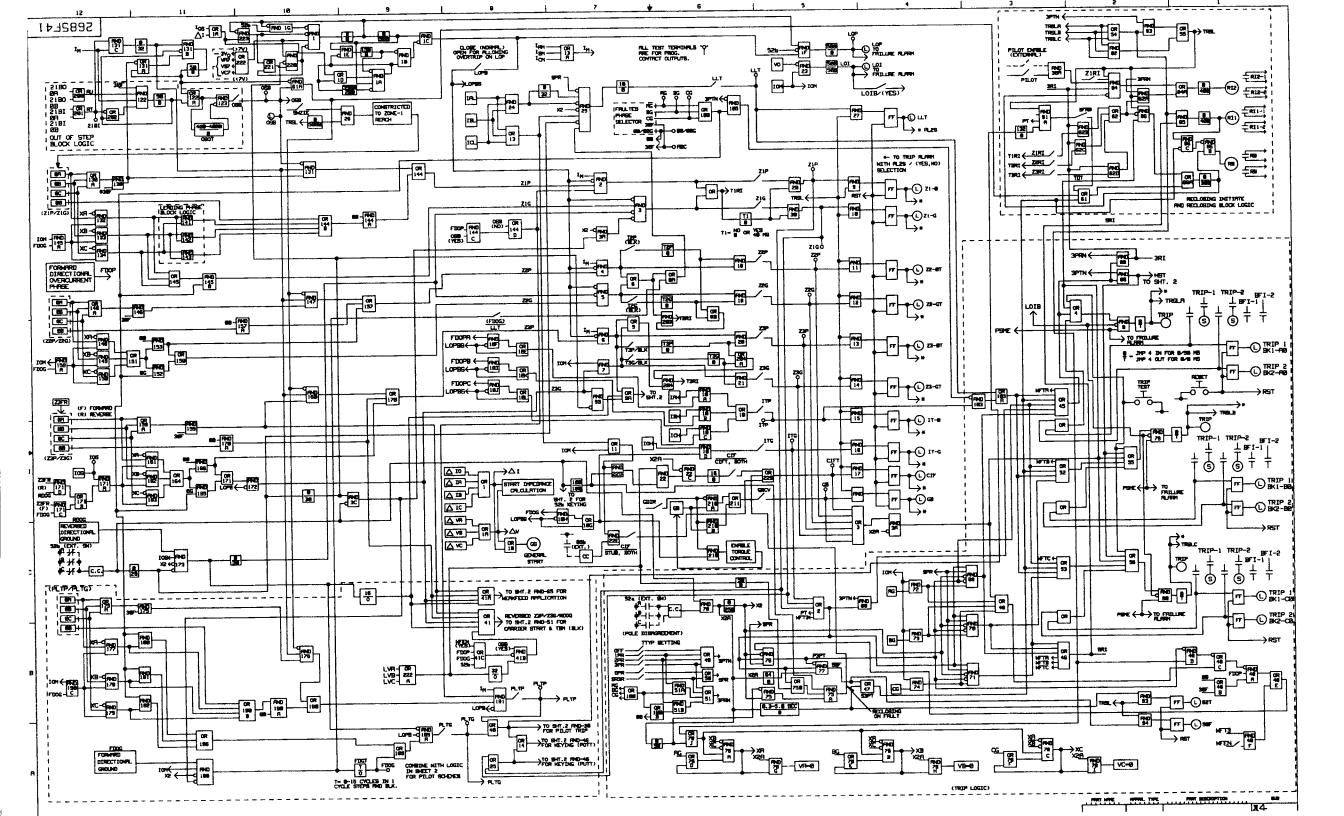

|   | J-2  | MDAR System Logic Diagram                                                       |

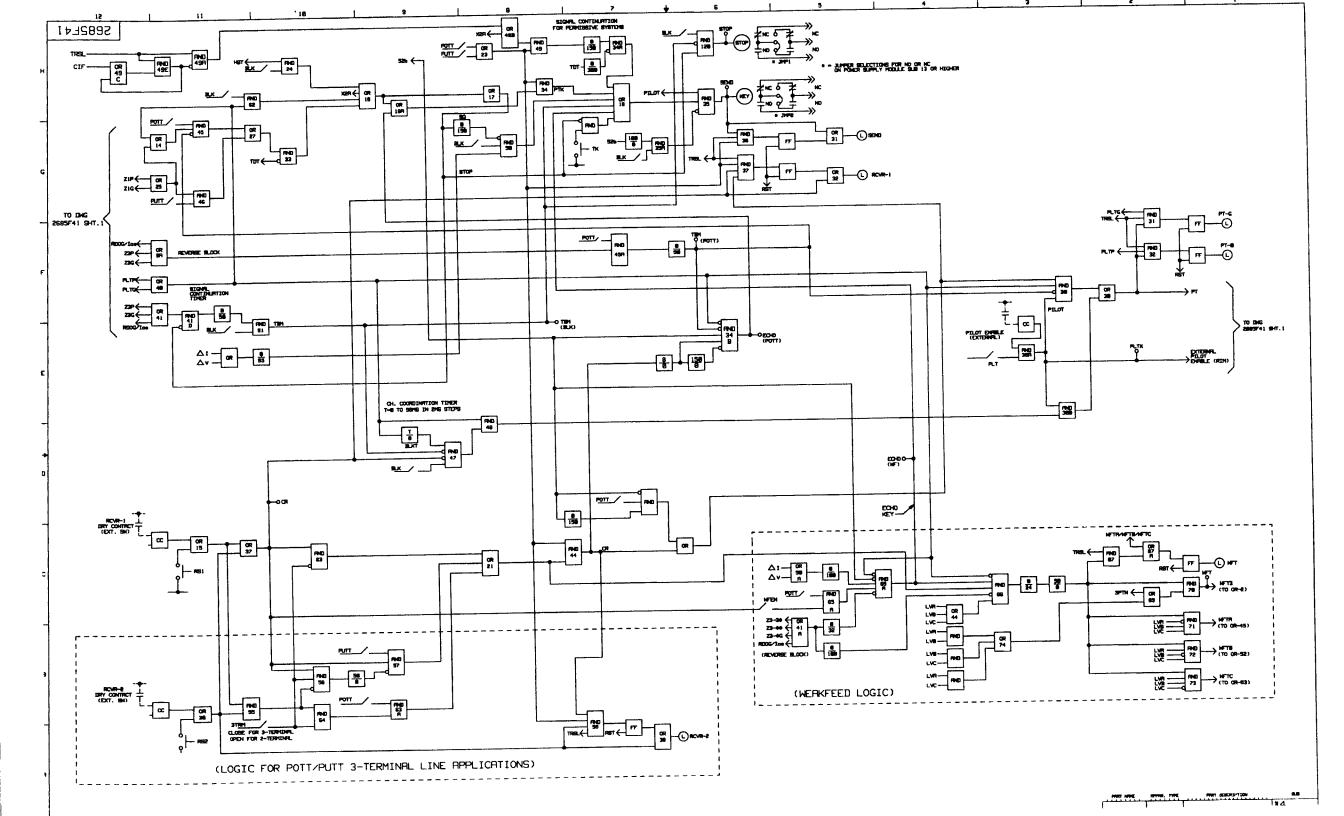

|   | J-3  | MDAR System Logic Diagram                                                       |

|   | J-4  | MDAR System Logic Diagram                                                       |

# TABLES

#### TABLE NO.

# PAGE

| 3-1 | MDAR Catalog Numbers                  |

|-----|---------------------------------------|

| 3-2 | MDAR Accessories                      |

| 3-3 | Single-Pole-Trip Operating Modes      |

| 3-4 | MDAR Programmable Output Contacts     |

| 4-1 | Setting Display                       |

| 4-2 | Metering Display                      |

| 4-3 | Target (Fault Data) Display           |

| 4-4 | Recommended Jumper Positions (V2.1X)  |

| 4-5 | Output Contact Selection              |

| 5-1 | Current Transformer Settings          |

| 5-2 | Reclosing Initiation Mode Programming |

| 5-3 | Trip Time Constants for Curves        |

| H-1 | MDAR Settings (Non-Pilot System)      |

| H-2 | Trip Time Constants for CO Curves     |

| H-3 | Fault Types Applied to MDAR           |

|     |                                       |

# Section 1. PRODUCT DESCRIPTION

#### 1.1 INTRODUCTION

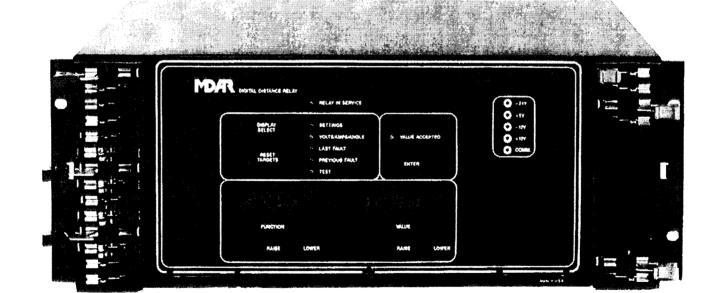

The MDAR relay assembly (**Figure 1-1**) is a numerical transmission line protection system, with three zones of distance protection. All measurements and logic are performed by digital means, using a microprocessor. Self-checking and line monitoring techniques are included. *MDAR is primarily recommended for application on non-series compensated lines.*

The non-pilot MDAR relay system is standard (**see Section 3**); an optional pilot MDAR relay system is also available (in **Section 3**).

#### 1.2 MDAR CONSTRUCTION

The standard nomenclature for **ABB** relay protection equipment is as follows:

- Cabinet contains fixed-racks, swing-racks, or open racks

- Rack contains one or more chassis (e.g., the MDAR)

- Chassis contains several modules (e.g., Microprocessor or Power Supply)

- Module contains a number of functional circuits (on printed circuit board)

- Circuit a complete function on a printed circuit board (e.g., analog-to-digital conversion)

- The MDAR relay assembly consists of an outerchassis and an inner-chassis which slides into the outer-chassis. The MDAR conforms to the following dimensions and weight (see also Section 2):

- Height 7" (requires 4 rack units; 1.75" each)

- Width 19"

- Depth 13.6"

- Weight 35 Lbs

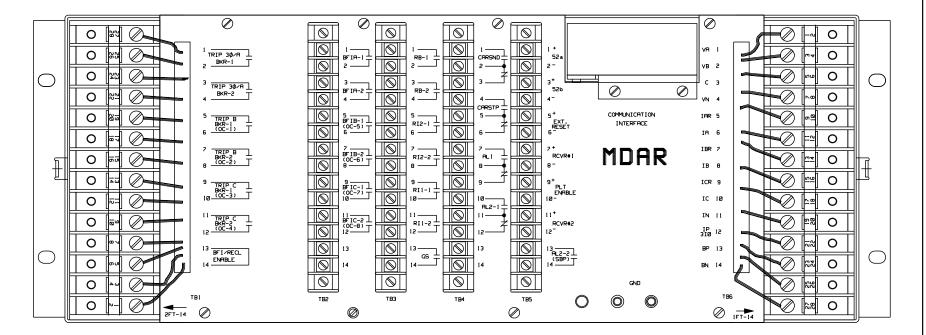

All of the relay circuitry, with the exception of the input isolation transformers and first-line surge protection, are mounted on the inner chassis, to which the front panel is attached. The outer chassis has a Backplate, which is a receptacle for all external connections, including a communication adaptor (**see Figure 4-1**). Two FT-14 switches may be included, as options, in the two peripheral areas of the outer chassis. The FT-14 switches permit convenient and safe disconnection of trip, ac and dc input circuits, and provide for injection of test signals.

The MDAR relay provides the following contact outputs:

- 4 make contacts (2 TRIP, 2 BFI); 8 additional optional contacts when Single-pole Trip option is used

- Single-pole Reclose Initiate (2 Form A)

- Three-pole Reclose Initiate (2 Form A)

- Reclose Block (2 Form A)

- General Start (1 Form A)

- System Failure Alarm (1 Form C)

- TRIP Alarm (1Form C; 1 Form A is available if SBP is not used)

- 8 additional programmable contacts when the Contact module is used

#### 1.3 MDAR MODULES

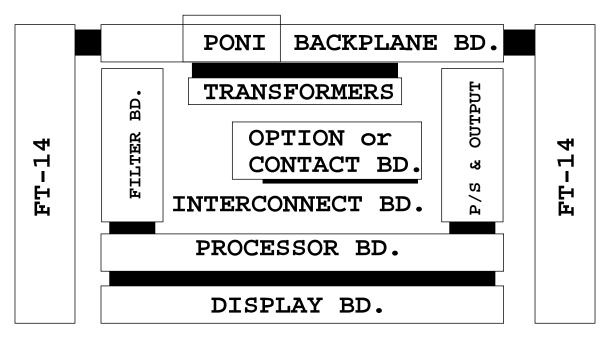

The inner and outer chassis, together, contain 6 standard modules, plus the option module for single pole trip applications (**see Figure 1-2**). The Backplate is connected to the Backplane module (outer chassis). The remaining modules are attached to the inner chassis:

- Interconnect module

- Option module or Contact module

- Filter module

- Microprocessor module

- Display module

- Power Supply module

Circuit descriptions for each module, may be found in **Appendices A thru G**, in accordance with the list in the Preface to this document (**see** "**Contents of Relay System**").

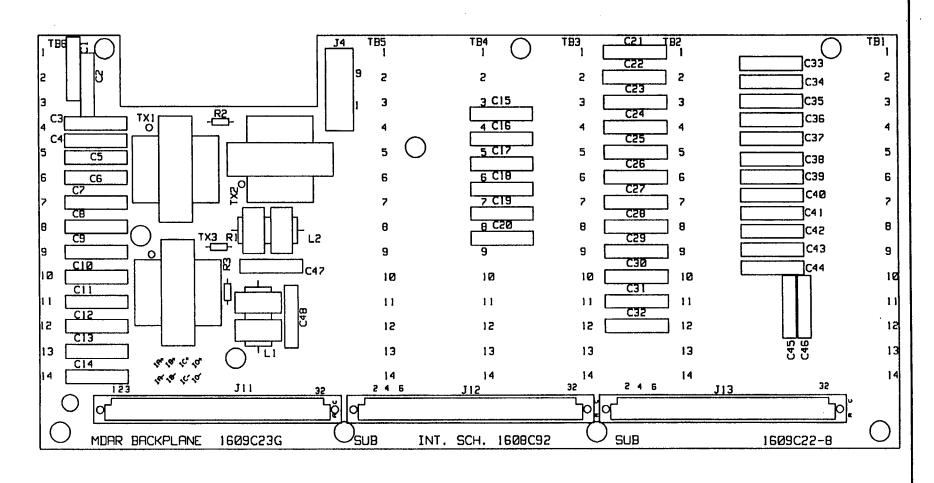

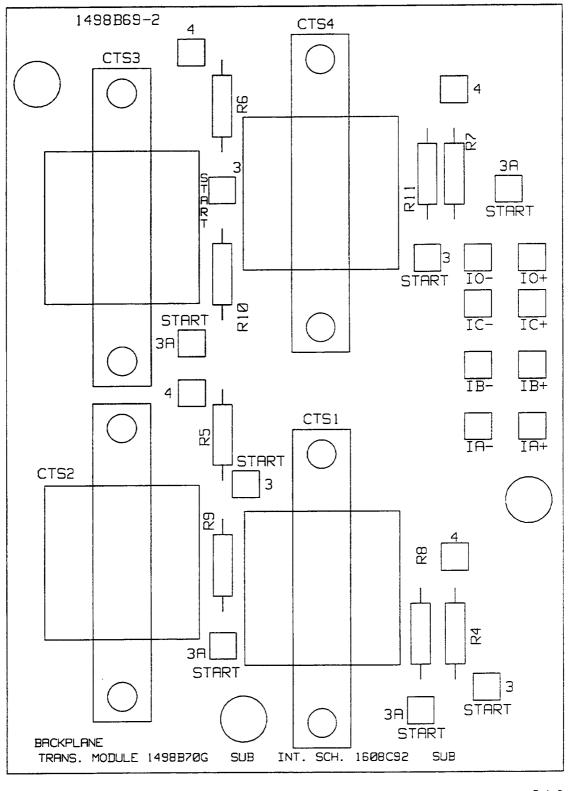

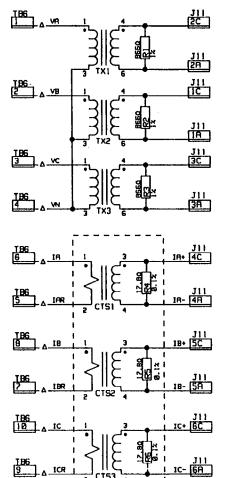

#### 1.3.1 Backplane Module

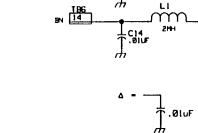

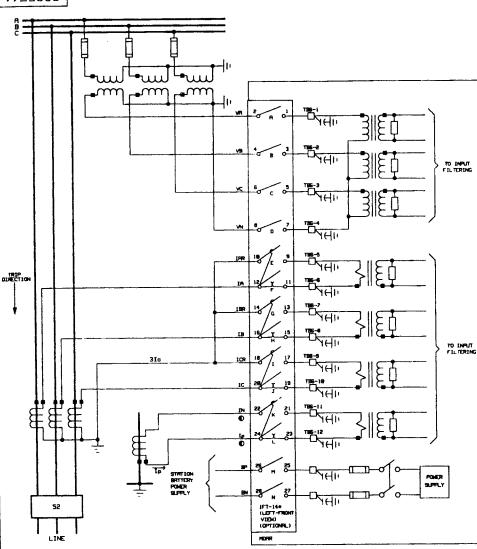

The Backplane Assembly includes three voltage transformers, four current transformers, two filter chokes and several surge protection capacitors.

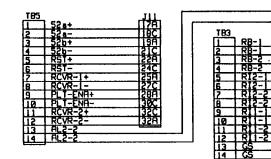

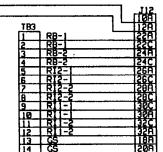

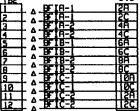

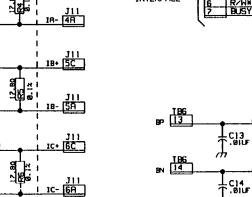

The Backplane Module (**see Appendix A**) receives all external connections (with or without the FT-14 switch option), and connects directly to the Interconnect module, thru plug-in connectors (J11, J12, J13) which provide the connection between outer and inner chassis.

The female parts of the connectors are mounted on the Backplane module, which is part of the outer chassis. The male parts of the connectors are mounted on the Interconnect module, which is part of the inner chassis.

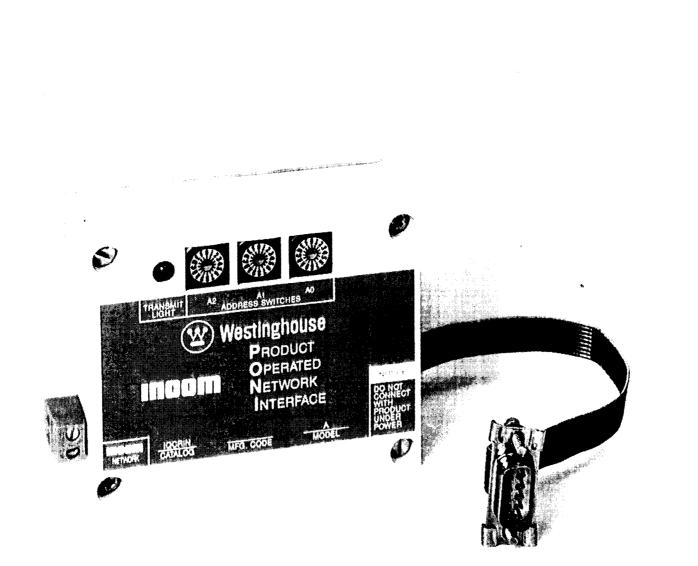

The INCOM<sup>®</sup> or RS232C PONI<sup>1</sup> (see Figure 1-3) is mounted on the backplate of the outer chassis and is connected to the Backplane module.

#### 1.3.2 Interconnect Module

The Interconnect module (**see Appendix B**) becomes the floor of the MDAR inner chassis; it provides electrical connections from and to all other modules: from the Backplane (at the rear), to the Filter and Power Supply modules (at left and right, respectively), and to the Microprocessor and Display modules at the front of the inner chassis.

The Interconnect module receives inputs  $V_{AN}$ ,  $V_{BN}$ ,  $V_{CN}$ ,  $I_A$ ,  $I_B$ ,  $I_C$ ,  $I_P$  from the Backplane module and feeds them to the Filter module. The IP input is used for zero-sequence dual-polarizing ground current measurement; the input is from the power transformer neutral ct. Also, seven opto-couplers, on the Interconnect module, send the following signals to the Microprocessor module:

- External Reset resets the front target display.

- **52b** used for close-into-fault (**CIF**) detection, load loss trip (**LLT**) and carrier-start and stop control in a pilot system.

- **52a** (for single-pole trip option; i.e., for pole disagreement).

- **Pilot Enable** should be "ON" for the pilot system option.

- **Receiver #1** (for Pilot option) carrier receiver for two terminal application.

- **Receiver #2** (for Pilot option) second carrier receiver for three-terminal application.

- SBP (89b) for stub bus protection.

#### 1.3.3 Option Module/Contact Module

For single-pole tripping applications, an Option module (**see Appendix C**) is added with extra tripping

and reed relays. The Option module plugs into the Interconnect module.

For 3-pole tripping application, an optional Contact module can be plugged into the connector and provide 8 additional programmable output contacts.

#### 1.3.4 Filter Module

The Filter module (**see Appendix D**) band-limits the seven inputs from the Interconnect module:  $V_{AN}$ ,  $V_{BN}$ ,  $V_{CN}$ ,  $I_A$ ,  $I_B$ ,  $I_C$ ,  $I_P$ . These inputs are fed to the Microprocessor module (analog signal multiplexer).

#### 1.3.5 Microprocessor Module

The Microprocessor module (**see Appendix E**) includes the following subsystems:

- <u>Microprocessor</u> Intel 80C196, a 16-bit microcontroller operating with a 10 MHz clock.

- **EPROM** Program memory in separate, easilyreplaced EPROM chips.

- **PROM** Programmable read-only memory.

- **RAM** Volatile read-write memory, for working storage.

- NOVRAM (EEPROM) Non-volatile memory for storing settings and fault-data targets when the MDAR relay is deenergized.

- <u>A/D Converter</u> The seven inputs from the Filter module are analog-multiplexed to a single sample/hold circuit. The output of the sample/hold is fed to the Analog-to-Digital Converter through an auto-ranging circuit which shifts gain by a factor of eight.

- Digital I/O Circuitry Status inputs from breaker auxiliary contacts (52a and 52b), and external reset signal are interfaced to the microprocessor via optical isolators (Figure 4-2). The microprocessor executes control outputs using dry contacts. Output relays (Figure 4-2) are used for breaker tripping, breaker failure initiation (BFI), reclose initiation (RI), and reclose blocking (RB). General start contact (GS) is provided for starting the external sequence of events or fault recorders. Trip and relay-failure alarm contacts are included. Reed relays in the trip circuits sense trip coil current flow and feedback target information to the microprocessor.

For the option of Contact module, eight additional output contacts are provided and can be programmed from 30 functions shown in **Table 3-4**.

<sup>&</sup>quot;INCOM "stands for INtegrated COMmunications. The "PONI" acronym stands for Product Operated Network Interface.

#### NOTE: JMP3 should be "OUT" for normal ABC rotation. Insert a jumper into JMP3 position for ACB phase rotation system application.

#### 1.3.6 Display Module

The Display module has two (four-digit) alphanumeric displays for settings, metering fault designation and information. The metering display shows threephase voltage, current and angle. Fault data, stored in the Microprocessor module, is accessible through the front panel display. Fault data includes: pre-fault phase A voltage, current and angle. It also shows the type of fault, fault voltages, currents, angles and fault location. The Display module is attached to the front panel (**see Figure 1-1**); it can be used to access and store data, and contains 7 LEDs, as follows:

- · Relay in Service (ready to use)

- Settings (can read or change settings)

- Volts/Amps/Angles (can read measuring inputs)

- Last Fault (when flashing, indicates new fault information available)

- Previous Fault (when last fault LED flashes twice/ minute, indicates information for the fault preceding the last fault)

- Value Accepted (when the Settings LED is also "ON", a new setting value is accepted; when the Test LED is also "ON", the output contacts can be tested)

- Test (can verify self-check and perform functional test)

The display will be blocked momentarily, every minute, for the purpose of self-check; this will not affect the relay protection function.

A display saver software is also built in. The MDAR display will be on only for 5 minutes after turning the dc power on or depressing any one of the front panel pushbuttons or detecting faults on the line.

#### 1.3.7 Power Supply Module

The Power Supply module (**see Appendix G**) is available in three ranges:

- 38 70 Vdc

- 88 145 Vdc

- 176 290 Vdc

Provides isolation from station battery; includes overcurrent and overvoltage protection. Status monitoring and loss-of-power indication are accomplished via a failure-alarm relay (on the Interconnect module). Relay is normally picked up, but the processor deenergizes it when a problem is found. Total power loss also drops-out the relay. Front-panel test points provide access to power-supply output voltages for test purposes:

- +12 Vdc

- -12Vdc

- -24 Vdc

- + 5 Vdc

#### 1.3.8 Contact Outputs

#### 1.4 TEST ACCESSORIES

The MDAR may be tested with two devices:

• Inner Chassis Test Fixture.

This device is similar to the outer chassis, and includes a Backplane and Transformer assembly.

Extender Board

This device includes two small pc boards with two ribbon cables. The inner chassis can be tested outside of the outer case by means of the Extender Board.

#### 1.5 FAULT DETECTION SOFTWARE

MDAR fault-detection software operates in two modes:

- Background mode

- Fault mode

The MDAR relay normally operates in the "Background mode" where it looks for phase current or phase voltage disturbances. Once a phase disturbance is detected, the relay enters the "Fault mode". During non-fault operation (in the Background mode), the MDAR Microprocessor (U100) used its spare time to check its hardware, service the operator panel, and check for a disturbance in voltage or current which indicates a possible fault. If a disturbance is seen, the programs switch to the Fault mode, for several power cycles or longer, to perform phase and ground unit checks for each zone and function.

#### 1.5.1 Background Mode

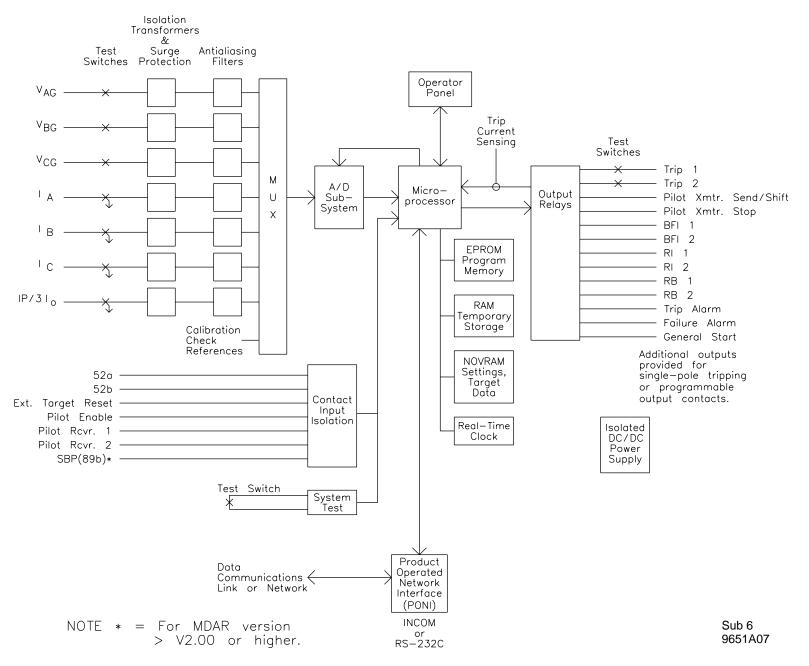

During the background mode, the seven inputs (currents and voltages shown in **Figure 1-4**) are sampled to test for line faults. These currents and voltages are sampled and converted into digital quantities and input to the Microprocessor where all signal processing takes place. (MDAR detects faults

by digital computation; not by analog.) The system continuously takes 8 samples per cycle. The components of the signals which are power system frequency are extracted.

The MDAR software which does the sampling has 8 states; these states correspond to the sampling rate (8 samples per cycle). Movement from state to state is controlled by a timer. The timer is loaded with a state time at the beginning of the state. The code executed within a state should be completed before the timer expires. The software then waits for the timer to time out.

The MDAR relay program functions are included in a flow chart loop (shown in **Figure 1-5**), which the Microprocessor repeats 8 times per power cycle. Most functions are performed all of the time, in the background mode, as shown. An important detail (not shown in **Figure 1-5**) is that many of the checks are broken into small parcels, so that the whole complement of tasks is performed over a one-cycle period (eight passes through the loop). Some of the checks are performed more than once per cycle.

The 60 Hz components are extracted from the samples (from each cycle) and converted to voltage and current phasor values using a Fourier notch-filter algorithm. An additional dc-offset correction algorithm reduces overreach errors from decaying exponential transients. During the process, the sum of squares of the inputs are accumulated to provide rms values of current and voltage. The Fourier coefficients and sums are calculated for computing the phase angles. The sum of squares and the sums of the Fourier coefficients are updated for each sample, using information from the previous seven samples, to provide a full cycle of data.

#### 1.5.2 Fault Mode and Restricted Fault Tests

Upon entry into the fault mode, the sums of the Fourier coefficients and sum of squares from the background mode are stored. New sums are obtained, using fault data, to which offset compensation has been applied.

To speed up tripping for severe faults, restricted fault testing is implemented. The last half cycle of background mode input samples and the first half cycle of fault mode input samples are used to compute the current and voltage vectors and rms values. No dc offset compensation is performed. High-set instantaneous overcurrent and Zone 1 distance unit tests are executed (**see Section 3.2**, MDAR Line Measurement). This will speed up tripping by as much as one cycle for high current faults.

Instantaneous overcurrent, inverse time overcurrent protection, and out-of-step blocking are also conducted during the fault mode and background mode.

For Zone-2 and Zone-3 faults (**see Section 3**), impedance computation and checking will continue throughout the specified time delay. The impedance calculation will be performed once every cycle, in the fault mode and background mode.

#### 1.5.3 Unique Qualities of MDAR

A unique characteristic of the MDAR system is its phase selection principle. It determines the sum of positive and negative sequence currents for each phase by a novel method which excludes the influence of pre-fault load current. From this information, the fault type can be clearly identified and the actual distance to the fault can be estimated.

High-resistance ground-fault detection is available in MDAR. Sensitive directional pilot tripping is achieved through an **FDOG** timer (**FDGT**), which is selectable from 0 to 15 cycles or block, on the Microprocessor module. The pilot distance unit is always active and has the priority for tripping.

Load-loss tripping entails high-speed, essentially simultaneous clearing at both terminals of a transmission line for all fault types except three-phase, without the need of a pilot channel.

Any fault location on the protected circuit will be within the reach of the zone 1 relays at one or both terminals. This causes direct tripping of the local breaker without the need for any information from the remote terminal. The remote terminal recognizes the loss of load-current in the unfaulted phase(s) as evidence of tripping of the remote breaker. This, coupled with Zone-2 distance or directional overcurrent ground fault recognition at that terminal, allows immediate tripping to take place at that terminal.

#### 1.6 SELF-CHECKING SOFTWARE

MDAR continually monitors its ac input subsystems using multiple A/D converter calibration-check inputs, plus loss-of-potential and loss-of-current monitoring described. Failures of the converter, or any problem in a single ac channel which unbalances nonfault inputs, trigger alarms. Self-checking software includes the following functions:

- a. Digital Front-end A/D Converter Check

- b. Program Memory Check Sum

Immediately upon power-up, the relay does a complete **ROM** (**EPROM**) checksum of program memory. Afterwards, the MDAR relay continually computes the program memory checksum.

c. Power Up RAM Check

Immediately upon power-up, the relay does a complete **ROM** test of the **RAM** data memory.

d. Nonvolatile RAM Check

All front-panel-entered constants (settings) are stored in nonvolatile **RAM** in three identical arrays. These arrays are continuously checked by the program. If all three array entrees disagree, a nonvolatile **RAM** failure is detected.

For failures which do not disable the processor, the cause of the problem can be read on the display.

The failure modes, represented by their corresponding bits (zero thru 5), are shown in the value field if the "Test" mode is selected by the "Display Select" pushbutton.

- Bit 0 External RAM Failure

- Bit 1 EEPROM Warning

- Bit 2 ROM (EPROM) Failure

- Bit 3 EEPROM Failure (Non-Volatile memory)

- Bit 4 Analog Input Circuit Failure

- Bit 5 Microprocessor Failure

- Bit 6 Setting Discrepancy

All bits are expressed in a HEX byte form. For example, if the display shows "Test 1B", whose binary representation is 00011011, this means that the relay failed the self-test in the area of External RAM (bit 0), EEPROM (one-out-of-three failure, bit 1), EEPROM (two-out-of-three failure, bit 3) and Analog Input Circuit (bit 4). Normally, the test mode should show "Test 0", meaning that the relay passed the self-test routines. Bit 6 is for the setting discrepancy detection. If the ordering information calls for single-pole trip option and the jumper #2 on Microprocessor module is on position "1-2", which is for the programmable output contacts, the MDAR will give the error of "TEST 40".

# 1.7 UNIQUE REMOTE COMMUNICATION (WRELCOM<sup>®</sup>) PROGRAM

Two optional types of remote interface can be ordered.

- RS232C for single point computer communication.

- INCOM<sup>®</sup> for local network communication.

A special software (WRELCOM<sup>®</sup>) program is provided for obtaining or sending the setting information to the MDAR. The MDAR front panel shows two fault events (last and previous), but thru the remote communication, 16 fault events and 16 records of intermediate target data can be obtained and stored. Each record of the intermediate target data contains 8-cycle information (1-prefault and 7 post-fault), with 7 analog inputs and 24 digital data (at the sampling rate of 8 per cycle). Refer to WRELCOM<sup>®</sup> manual for detailed information.

#### 1.8 POWER SYSTEM ROTATION ABC OR ACB SELECTION

The phase rotation ABC or ACB can be selected by a jumper #3 on the Microprocessor module. The system indicates ABC rotation without jumper #3. With jumper #3 in place, the input phase sequence should be ACB, e.g., phase A leads phase C, C leads B and B leads A, respectively. The rotation is shown on the Metering Mode.

Check jumper #3 before energizing the relay. Normally, it should be removed for phase sequence rotation ABC.

esk00305

Figure 1-2 Layout of MDAR Modules Within Inner and Outer Chassis

(9/94)

I.L. 40-385.4A

esk00223

Figure 1-5 MDAR Relay Program Functions

# Section 2. SPECIFICATIONS

| 2.1 TECHNICAL                                                                |                                                                |

|------------------------------------------------------------------------------|----------------------------------------------------------------|

| Operating Speed<br>(from fault detection<br>to trip contact close<br>-60 Hz) | 12-14 ms (minimum)<br>22 ms (typical)                          |

| ac Voltage (VLN) at 60 Hz<br>(VLN) at 50 Hz                                  | 70 Vrms<br>63.5 Vrms                                           |

| ac Current (In)                                                              | 1 or 5 A                                                       |

| Rated Frequency                                                              | 50 or 60 Hz                                                    |

| Maximum Permissible ac Voltage                                               |                                                                |

| Continuous                                                                   | 1.5 x nominal voltage                                          |

| 10 Second                                                                    | 2.5 x nominal voltage                                          |

| Maximum Permissible ac Current                                               |                                                                |

| Continuous                                                                   | 3 x Nominal Current                                            |

| 1 Second                                                                     | 100 x Nominal Current                                          |

| Typical Operating Current                                                    | 0.5 A                                                          |

| dc Battery Voltages                                                          |                                                                |

| Nominal<br>48/60 Vdc<br>110/125 Vdc<br>220/250 Vdc                           | Operating Range<br>38 - 70 Vdc<br>88- 145 Vdc<br>176 - 290 Vdc |

| dc Burdens: Battery                                                          | 7 W normal<br>30 W tripping                                    |

| ac Burdens:                                                                  |                                                                |

| Volts per Phase                                                              | 0.02VA at 70 Vac                                               |

| Current per Phase                                                            | 0.15VA at 5 A                                                  |

#### 2.2 EXTERNAL CONNECTIONS

Terminal blocks located on the rear of the chassis suitable for #14 square tongue lugs

Wiring to FT-14 switches suitable for #12 wire lugs

#### 2.3 CONTACT DATA

Trip Contacts - make & carry 30 A for 1 second, 10 A continuous capability, break 50 watts resistive or 25 watts with L/R = .045 seconds

• Non-Trip Contacts

1A Continuous

0.1A Resistive Interrupt Capability

Supports 1000 Vac across open contacts

Contacts also meet IEC - 255-6A, IEC - 255-12, IEC -255-16, BS142-1982.

#### 2.4 MEASUREMENTS

Number of zones: 3 zones are standard (optional pilot adds additional zone).

Operating Characteristics: variable mho characteristics for all fault types.

#### 2.5 MEASUREMENT UNITS

Three variable mho phase-to-earth units and one variable mho phase-to-phase impedance unit per zone.

One ground directional (ITG) and one phase directional (ITP) high-set overcurrent unit.

Three-phase non-directional overcurrent units (IL) for load loss trip and CIFT.

One non-directional phase overcurrent unit medium set (Im) for phase supervision.

One non-directional ground overcurrent unit medium set (IOM) for ground supervision.

One ground overcurrent unit for LOI monitoring.

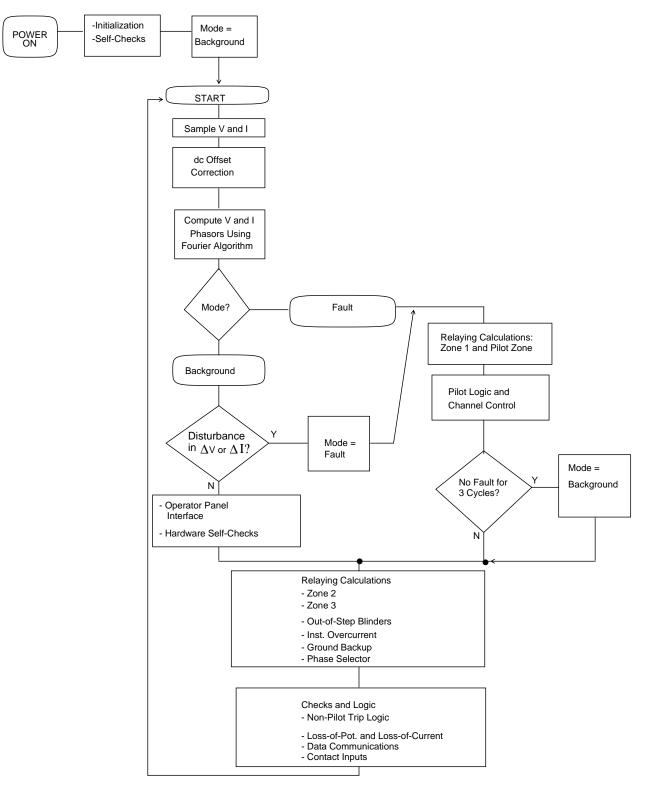

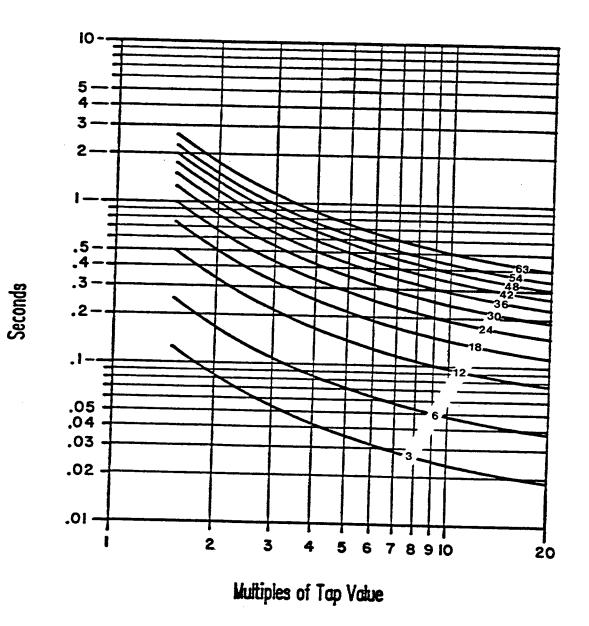

One inverse time overcurrent ground unit with CO characteristics (**see Figures 2-1 thru 2-7**); selectable non-directional or directional capability.

One forward set instantaneous directional overcurrent ground unit. (Pilot-high resistance ground faults.)

Three under-voltage units (LV) for weakfeed and LOP supervision.

Four current change fault detectors, and three voltage change fault detectors.

One instantaneous overcurrent unit low set (IOS)

One reverse set instantaneous directional overcurrent ground unit (Pilot Carrier Start, Weakfeed, Transient Blocking)

#### 2.6 SETTING RANGES

Phase and Ground Distance (Zone 1, 2, 3):

- 0.01-50 ohms in 0.01 ohm steps for 5 A (ct)

- 0.05-250 ohms in 0.05 ohm steps for 1 A (ct)

Zone Timers - Separate timers for phase and ground:

- Zone-1 (No/Yes; 2 cycle delay if Yes is selected)

- Zone-2 (0.10 to 2.99 seconds in 0.01 second steps, Block)

- Zone-3 (0.10 to 9.99 seconds in 0.01 second steps, Block)

Forward Directional Ground Timer (FDGT)

• 0 to 15 cycles in 1 cycle steps, Block Ohms per Unit Distance

• 0.300-1.500 in 0.001/DTYP (Km or Mi)

Inverse Time Overcurrent Ground Relay:

- Pickup (0.1-0.8) in 0.1 A increments for 1 A (ct).

- Pickup (0.5-4.0) in 0.5 A increments for 5A (ct). Choice of 7 time-curve families (CO-2, 5, 6, 7, 8, 9, 11 Characteristics), 63 time curves per family. (See Figures 2-1 thru 2-7.)

- Set for directional or non-directional operation.

High set instantaneous directional overcurrent trip units - phase and ground ( $I_{AH}$ ,  $I_{BH}$ ,  $I_{CH}$ ,  $I_{OH}$ ).

- 2.0-150 in 0.5 A steps for 5 A (ct)

- 0.4-30 in 0.1 A steps for 1 A (ct)

#### 2.7 GROUND/ PHASE OVERCURRENTS AND UNDERVOLTAGE UNITS

- Undervoltage level units (LVA, LVB, LVC and CIF) for weakfeed and close-into-fault, from 40 to 60 Vrms in 1-volt steps.

- Current Units (IAL, IBL, ICL, IOS, IOM & IM)

0.5 10 in 0.5 A steps for 5 A (ct)

0.1 2 in 0.1 A steps for 1 A (ct)

Current Change Fault Detectors ( $\Delta I_A, \Delta I_B, \Delta I_C$ , and  $\Delta I_0$ ), no setting required.

Voltage change fault detectors (  $\Delta V_A,\, \Delta V_B$  and  $\Delta V_C)$  no setting required

Ground Overvoltage Unit  $3V_0$  (no setting required).

#### 2.8 OPTIONAL SINGLE-POLE-TRIP LOGIC AND OUTPUTS (Without Programmable Contact Option)

- 3PT/RB if reclosing on a permanent fault

- 3PT/RB if second phase(s) fault during single phasing

- 3PT on a selectable time delay limit if the system fails to reclose (62T)

- TRIP/RI mode selections (TTYP):

| <u>SELECT</u> | TRIP     | <u>RI</u>     |

|---------------|----------|---------------|

| OFF           | 3PT      | NO            |

| 1PR           | 3PT      | RI2(¢G)       |

| 2PR           | 3PT      | RI2(¢G,¢¢)    |

| 3PR           | 3PT      | RI2(¢G,¢¢,M¢) |

| SPR           | SPT (øG) | RI1           |

|               | 3PT (Mø) | NO            |

| SPR/3PR       | SPT (øG) | RI1           |

|               | 3PT (Mø) | RI2           |

|               |          |               |

#### Legend:

- SPT Single Pole Trip

- 3PT 3-Pole Trip

- RI Reclose Initiation

- RB Reclose Block

- RI2 3-Pole Reclose Initiate

- RI1 Single Pole Reclose Initiate

- φG Single Phase to Ground Faults

- Mo Multi-Phase Faults

- φφ 2-Phase Faults

#### 2.9 OPTIONAL PROGRAMMABLE OUTPUT CONTACTS (Without Single-pole Trip Option)

Eight programmable contacts selected from 30 preassigned signals which can be programmed either AND or OR logic together. (**Refer to Table 3-4** for the 30 signals.)

• Four NO heavy duty contacts with FT-switches and 1 timer for pickup and/or dropout delay (0 to 5 sec. in 0.01 steps)

• Four Standard contacts with jumper selection for NO or NC outputs and one timer for pickup and/or dropout delay. (0 to 5 sec. in 0.01 sec/step).

#### 2.10 OUT-OF-STEP BLOCK

- OSB Override Timer 400-4000 ms in 16 ms steps

- OSB Inner Blinder (RT) 1.0-15.0 ohms in 0.1 ohm steps

# NOTE: The RT is a standard setting; for load restriction.

OSB Outer Blinder (RU) 3.0-15.0 ohms in 0.1 ohm steps

# 2.11 SELECTABLE PHASE SEQUENCE ABC OR ACB ROTATION

A jumper #3 on Microprocessor module is used for phase rotation selection.

- ABC system without jumper #3

- ACB system with jumper #3 in place

#### 2.12 OPTIONAL COMMUNICATION INTERFACE

- RS-232C PONI for single point computer communications

- INCOM<sup>®</sup>/PONI for local network communications

#### 2.13 CHASSIS DIMENSIONS AND WEIGHT

Height 7" (177.8mm), 4 Rack Units (**See Figure 2-8**) Width 19" (482.6mm) Depth 14" (356mm) including terminal blocks Weight 35 lb. (16Kg net)

#### 2.14 ENVIRONMENTAL DATA

Ambient Temperature Range

- For Operation -20°C to +60°C

- For Storage -40°C to +80°C

Dielectric Test Voltage 2.8 kV, dc, 1 minute (ANSI C37.90.0, IEC 255-5)

Impulse Withstand Level 5 kV peak, 1.2/50  $\mu sec,\, 0.5$  joule (IEC 255-5)

Fast Transient Surge Withstand Capability 4 kV, 5/ 50 nsec (IEC 801-4); 5kV 10/150 nsec (ANSI C37.90.1)

Oscillatory Surge Withstand Capability 2.5 kV, 1 MHz (ANSI C37.90.1, IEC 255-6)

EMI Volts/Meter Withstand 25 MHz-1GHz, 10V/m Withstand (Proposed ANSI C37.90.2).

Sub 2 619596

Figure 2-1 CO-2 Curve Characteristics

Builtiples of Tap Value

Sub 2 619597

Seconds

Multiples of Tap Value

Sub 2 619598

Figure 2-3 CO-6 Curve Characteristics

Multiples of Tap Value

Sub 2 619599

Figure 2-4 CO-7 Curve Characteristics

(11/92)

Seconds

Seconds

Multiples of Tap Value

Sub 2 619600

Multiples of Tap Value

Sub 2 619601

Figure 2-6 CO-9 Curve Characteristics

-

Sub 2 619602

Figure 2-7 CO-11 Curve Characteristics

NOTE: REFER TO SYSTEM DRAWING FOR THE EXTERNAL WIRING.

#### Section 3. APPLICATIONS AND ORDERING INFORMATION

## WARNING

Before energizing the relay, check jumper #3 on the Microprocessor module for phase sequence rotation ABC or ACB. Remove jumper #3 for system ABC rotation. Refer to Section 1.8 for ACB system.

#### 3.1. NON-PILOT SYSTEM

The MDAR non-pilot relay system detects faults in three zones of distance, phase and ground. Zones-1 and 2 are forward set; Zone-3 can be set to forward or reverse. There is also a separate optional pilot zone (**see Section 3.5**). The fault locator can be set to indicate fault distance in miles or kilometers.

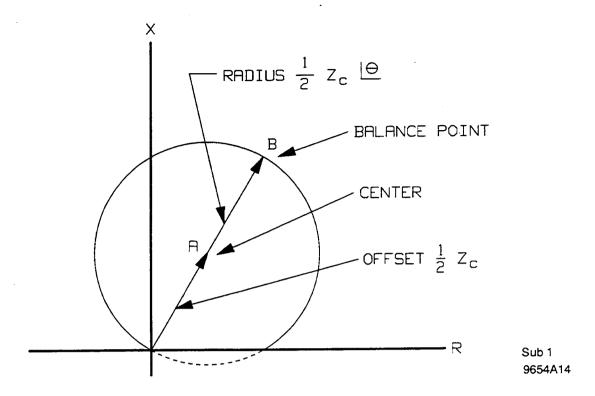

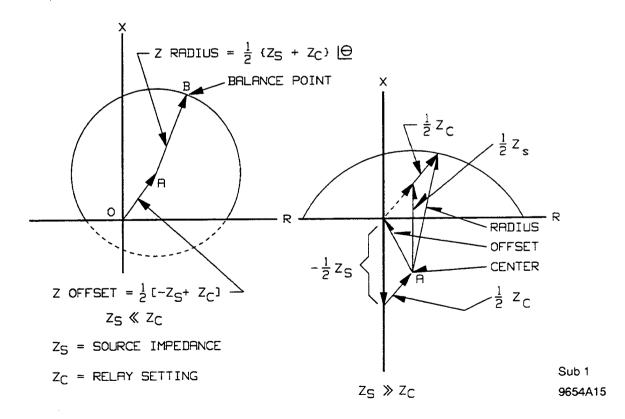

The R-X Diagram (shown in Figure 3-1) describes the characteristics available with MDAR. Zone-1 phase and ground settings are chosen to provide substantial coverage of the protected line without overreaching the next bus. A setting of 80% of the line impedance is typical. Faults occurring within the reach of the Zone-1 measurement cause direct tripping without regard to any action occurring at the remote terminal. Zone-2 settings are chosen to assure that faults occurring on the next bus are recognized. Settings are chosen (independent of the Zone-1 settings), generally to be 120 to 150% of the line impedance. Any fault occurring on the protected line will be recognized by this Zone-2 measurement (within the fault resistance and current limitations of the relaying system). Zone-2 tripping occurs with time delay (T2) or, where equipped with pilot provisions, at high speed, subject to the constraints imposed by the pilot channel for the particular pilot system selected. The Zone-3 measurement is directional, and may be chosen to respond to forward or reverse faults. The reverse sensing option is chosen for the blocking system where the reverse fault carrier start function is required. It is also used in conjunction with the T3 trip function, chosen to coordinate with adjacent terminal Zone-2 timing. The forward sensing option produces time delayed backup to other devices sensing forward faults. Blinder measurements (B1, B2, B3, B4) are available for out-of-step sensing. The inner blinder (as a standard function) also restricts the trip zone of each of the 3-phase fault measuring units.

#### 3. 2. LINE MEASUREMENT TECHNIQUES

Line measurement techniques applied to each zone include:

- Single-Phase-To-Ground fault detection

- 3-Phase fault detection

- Phase-to-Phase fault detection

- Phase-to-Phase-to-Ground fault detection

- NOTE: IOM is used to supervise all ground units and IM is used to supervise all phase units, including Zone -1,2,3 and pilot for tripping.

#### 3.2.1 Single-Phase-to-Ground

Single-phase-to-ground fault detection (**see Figure 3-2**) is accomplished by 3 quadrature polarized phase units ( $\phi$ A,  $\phi$ B,  $\phi$ C). Equations 1 and 2 (below) are for operating and reference quantity, respective-ly. The unit will produce output when the operating quantity leads the reference quantity.

$$V_{XG} - [I_X + k_0 I_0] Z_{CG}$$

<sup>(1)</sup>

$$\mathbf{k}_0 = \frac{\mathbf{z}_{\mathsf{oL}} - \mathbf{z}_{1\mathsf{L}}}{\mathbf{z}_{1\mathsf{L}}} = \mathsf{ZR}\angle(\mathsf{GANG} - \mathsf{PANG}) - 1$$

$$\mathbf{I}_0 = \frac{1}{3}(\mathbf{I}_{\mathsf{A}} + \mathbf{I}_{\mathsf{B}} + \mathbf{I}_{\mathsf{C}})$$

Vector (V<sub>O</sub>)

where  $V_{XG} = V_{AG}$ ,  $V_{BG}$ , or  $V_{CG}$

$$I_X = I_A, I_B \text{ or } I_C$$

- $Z_{1L}, Z_{0L}$  = positive and zero sequence line impedance in relay ohms.

- $Z_{CG}$  = Zone reach setting in secondary ohms of  $Z_{11}$  for  $\phi$ GF fault

- $V_Q$  = quadrature phase voltages, i.e.,  $V_{CB}$ ,  $V_{AC}$  and  $V_{BA}$  for  $\phi A$ ,  $\phi B$  and  $\phi C$ units, respectively.

#### 3.2.2 Three-Phase

Three-phase fault detection (**see Figure 3-3**) is accomplished by the logic operation of one of the three

(2)

ground units, plus the  $3\phi F$  output signal from the faulted phase selector unit.

However, for a 3-phase fault condition, the computation of the distance units will be:

$$V_{XG} - I_X Z_{CP} \tag{3}$$

and

$$(V_Q)$$

(4)

where  $V_{XG} = V_{AG}$ ,  $V_{BG}$ , or  $V_{CG}$

- $I_X = I_A, I_B \text{ or } I_C$

- $Z_{CP}$  = Zone reach setting (PLTP, Z1P Z2P, and Z3P) in secondary ohms of Z<sub>11</sub> for multi-phase faults.

- $V_Q$  = Quadrature phase voltages, i.e.,  $V_{CB}$ ,  $V_{AC}$  and  $V_{BA}$  for  $\phi A$ ,  $\phi B$  and  $\phi$ C units, respectively.

If the MDAR detects that all three voltages are less than 1 volt, the pre-fault voltages (memory action) are used as reference for Zone-1 tripping. For Zone-2 and Zone-3, the memory action is in effect if all three voltages are less than 7 volts.

#### 3.2.3 Phase-to-Phase

The phase-to-phase unit (**see Figure 3-4**) responds to all phase-to-phase faults, phase-to-phase-toground faults, and some single-phase-to-ground faults. Equations (5 and 6) are for operating and reference quantity, respectively. They will produce output when the operating quantity leads the reference quantity.

$(V_{AB} - I_{AB}Z_{CP})$ (5)

$(V_{CB} - I_{CB}Z_{CP}) \tag{6}$

#### 3.3 MEASUREMENT ZONES

MDAR performs line measurement within 3 zones of the transmission line (Zone-1, Zone-2, Zone-3), and one optional pilot zone. When the MDAR functional display "STYP" is set at "3ZNP", it will perform the 3zone non-pilot function.

When the MDAR trips, the trip contacts will be sealed-in as long as the trip coil current flow exists. The trip contacts can be delayed dropout (by 50 ms) after the trip current is removed, providing a jumper (JMP4) on the Microprocessor module is connected.

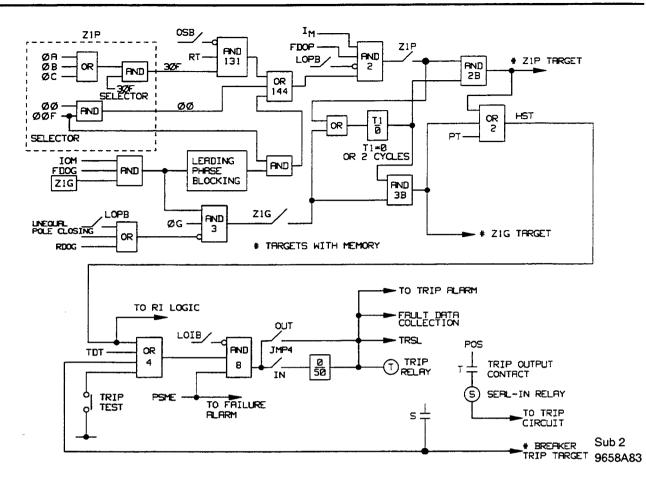

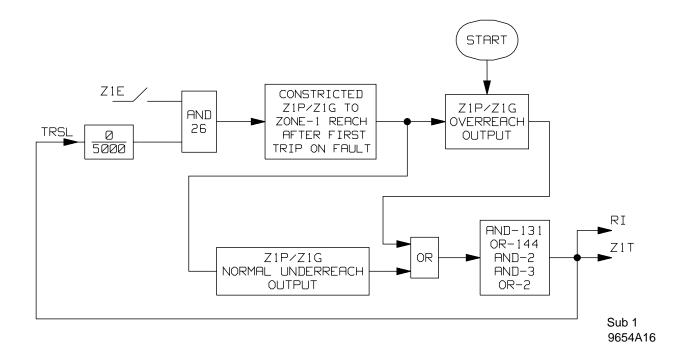

#### 3.3.1 Zone-1 Trip

For Zone-1 phase faults, the Z1P unit will identify the fault and operate. The 36 fault logic is supervised by the load restriction logic via AND131C and AND 131 (Figure 3-18a) and is also supervised by the selectable OSB, as shown in Figure 3-5. Outputs of Z1P and IM satisfy AND-2 and provides a high-speed trip (HST) signal from OR-2 to operate the trip output telephone relay. The trip circuit is monitored by a seal-in reed relay (S), which is in-series with each trip contact in the tripping circuits. The S relay will pick up if the trip current is higher than 0.5 Amp. The operation of the "S" contact will turn-on the breaker trip indicators (with memory), and feeds back to OR-4 to hold the trip relay in operation until the breaker trips and 52a contact opens (not shown in Figure 3-5). The TRSL signal plus the output signal from AND-2 turns on the Zone-1 phase trip indicator (Z1P). The breaker trip and Zone-1 phase trip indicators are memorized. They can be reset by external RESET voltage or through remote communication. By pushing the RESET pushbutton, the flashing LED will be reset, but the fault information will still remain in memory.

NOTE: The operating time of the Trip relay is 2 ms and the BFI relay is between 10 and 15 ms. The difference of the pickup times should be compensated in the breaker failure scheme.

The Z1P 3¢ trip logic AND-131 is supervised by both the conventional OSB and the subsequent OSB logic when the OSB is set to "YES", for more security on some special power system applications. ZIP logic AND-2 is also supervised by the FDOP (Forward Directional Overcurrent Phase unit) when the OSB is set to "YES" for more security on some special power system applications.

Similar operations exist for Zone-1 single-phase-toground faults. The Z1G unit sees the fault and operates; the IOM and FDOG units also operate, satisfying AND-3. Tripping occurs via OR-2 with Zone-1 ground trip indication Z1G. Logic AND-3 is also supervised by the signal of RDOG (reverse directional overcurrent ground) for security purposes.

The Z1G unit is also supervised by the signal of unequal-pole-closing and RDOG.

A two-out-of-three "leading phase blocking" logic is included for solving the overreach problem of the single-phase ground distance units, which may respond to a  $\phi\phi G$  fault.

The high-speed trip (HST) signal also is connected to the reclosing initiation logic.

Either or both Zone-1 phase and Zone-1 ground function(s) can be disabled by setting the Z1P and/ or Z1G to the "OUT" position. Zone-1 trip can be delayed by setting T1 = YES. The delay time is 2 cycles for a non-pilot 3PT backup, with another system operating in SPT mode.

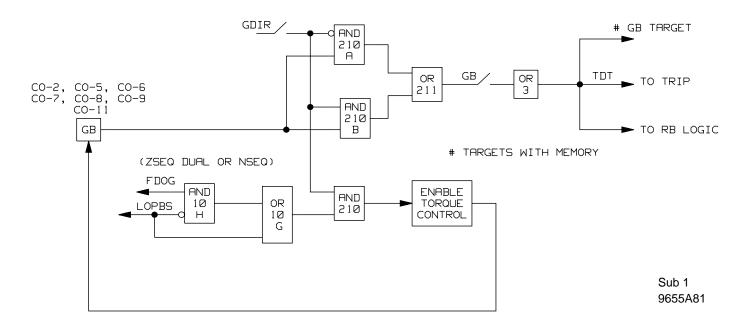

#### 3.3.2 Zone-2 Trip

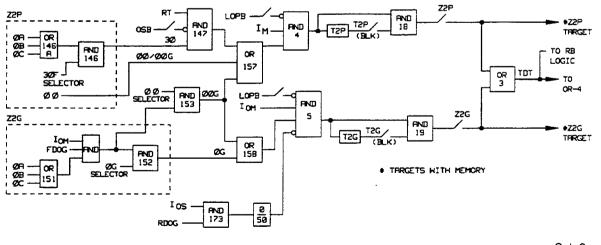

For Zone-2 phase faults, the Z2P unit will see the faults plus the output of IMoperate the Zone-2 phase timer (T2P). AND-4 output plus the T2P timer output satisfy AND-18, **as shown in Figure 3-6**. The AND-18 output provides time delay trip signal TDT via OR-3. Signal TDT picks up OR-4 (**Figure 3-5**) and operates the trip relay. The tripping and targeting are similar as described in Zone-1 trip except for Zone-2 phase time delay trip indicator (Z2P).

Similar operation occurs for Zone-2 single-phase-toground faults. The Z2G unit sees the fault and operates. This, plus the operation of the IOM, FDOG and T2G satisfy AND-19, and provide the TDT signal via OR-3 with Zone-2 ground time delay trip indicator (Z2G).

The single-phase ground distance units may respond to a  $\phi\phi G$  fault. The output of the Z2G unit plus the operation of the  $\phi\phi$  selection will trip the Z2P via OR-157, T2P and AND-18. Leading phase blocking is unnecessary for an overreach Zone device.

The TDT signal can be connected to the reclosing block logic. The settings for Zone-2 timers (phase and ground units) are independent, as follows:

- T2P (Zone-2 phase)

- T2G (Zone-2 ground)

The range of the timers is as follows:

• T2P and T2G (0.1 to 2.99 seconds or Block)

Either or both Zone-2 phase and Zone-2 ground function(s) can be disabled by setting Z2P and/or Z2G to the BLK position.

#### 3.3.3 Zone-3 Trip

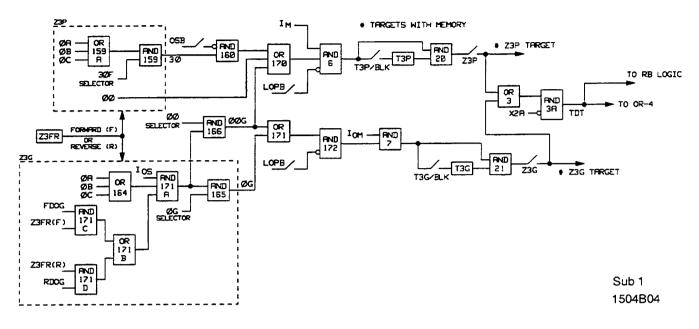

For Zone-3 phase faults, the Z3P (forward or reverse looking, depending on the Z3FR setting) unit will identify the faults, plus the IMIm output will operate the Zone-3 phase timer T3P. AND-6 output plus the T3P timer output satisfy AND-20 (**as shown in Figure 3-7**). The AND-20 output provides time delay trip signal (TDT) via OR-3. Signal TDT picks up OR-4 (**Figure 3-5**) and operates the trip relay. The tripping and targeting are similar to Zone-1 trip, except for the Zone-3 phase time delay trip indicator (Z3P).

For Zone-3 single-phase-to-ground faults, Z3G identifies the fault and operates. This, plus the operation of the IOM, satisfies AND-7; the TDT signal then trips via OR-3 with Zone-3 ground time delay trip indicator Z3G. The TDT signal can be connected to the reclosing block logic. For security, the Z3G unit is also supervised by the signal of FDOG when it is set for forward looking (or by the signal of RDOG when it is set for reverse looking) via logic OR-171B, AND-171C or AND 171D (**as shown in Figure 3-7**).

A similar operation for  $\phi\phi G$  faults (shown in Zone-2), is applied to Zone-3, through OR-170, T3P and AND-20 gates.

The settings for Zone-3 timers (phase and ground units) are independent, as follows:

- T3P (Zone-3 phase)

- T3G (Zone-3 ground)

The range of the timers is as follows:

• T3P and T3G (0.1 to 9.99 seconds or Block)

Either or both Zone-3 phase and Zone-3 ground function(s) can be disabled by setting Z3P and/or Z3G to the BLK position.

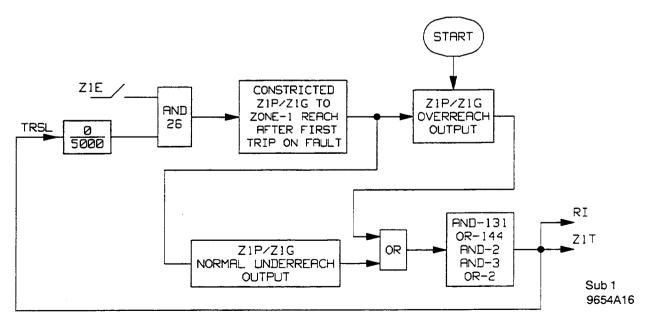

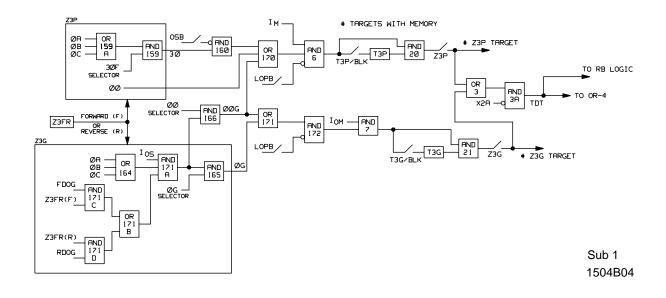

#### 3.3.4 Zone-1 Extension

This scheme provides a higher speed operation on end zone faults without the application of pilot channel.

If the MDAR functional display "STYP" is set on Z1E position, the Z1P/Z1G unit will provide two outputs: one is overreach which is set at 1.25 x Z1 reach by the microprocessor, and one is the normal Z1 reach. A single shot instantaneous reclosing device should be used when applying this scheme. The targets Z1P/Z1G will indicate either Z1 trip and/or Z1E trip

operations. The other functions (e.g., Z2T, Z3T, ac trouble monitoring, overcurrent supervision, ITP, ITG, CIF, unequal-pole closing load pickup control, load-loss acceleration trip, etc.) would remain the same as in the basic scheme (3ZNP).

For a remote internal fault (**refer to Figure 3-8**), either Z1P or Z1G will see the fault since they are set to overreach. High speed trip will be performed via the normal Z1T path (**Figure 3-5**), i.e., AND-2 (or AND-3), OR-2. HST signal operates the instantaneous reclosing scheme. The breaker recloses and stays closed if the fault is automatically cleared.

Target Z1P and/or Z1G will be displayed. Once the breaker trip circuit carries current, it operates the logic OR-5 (not shown), produces output signal TRSL, and satisfies logic AND-26 for 5000 ms (**Figure 3-8**). The output signal of AND-26 will trigger the Z1P/Z1G reach circuit, constricting their reaches back to the normal Zone-1 for 5000 ms. During the reach constricting periods, if the breaker is reclosed on a Zone-1 permanent fault, it will retrip again. If the breaker is reclosed on an end-zone permanent fault, the normal Z2T will take place.

For a remote external fault, either Z1P or Z1G will see the fault since they are set to overreach. High speed trip will be performed. HST signal operates the instantaneous reclosing scheme. The breaker recloses and stays closed if the fault has been isolated by the adjacent line breaker. However, if the adjacent line breaker fails to trip, the normal remote back up will take place.

NOTE: The reaches of Z1E are based on the Zone-1 settings multiplied by a factor of 1.25 (e.g., 1.25 x Z1P and 1.25 x Z1G).

#### 3.4 MDAR NON-PILOT FEATURES

The following features are standard with the Non-Pilot MDAR

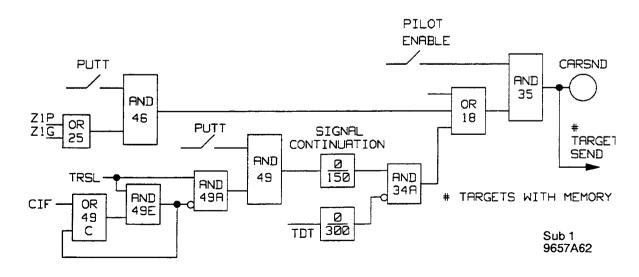

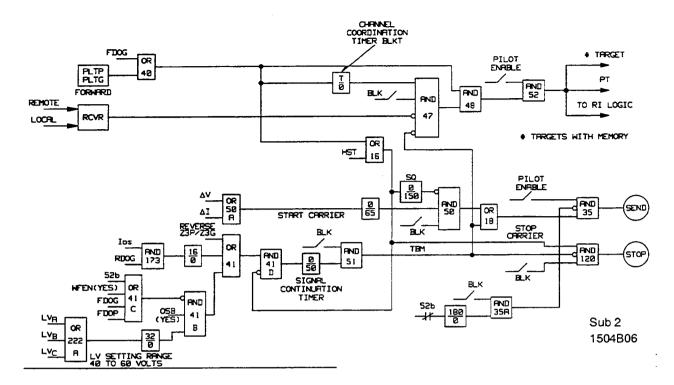

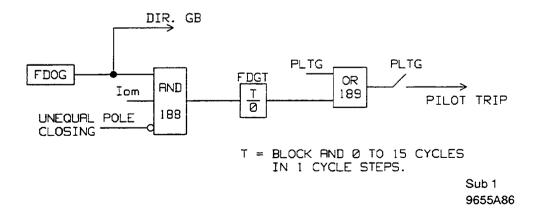

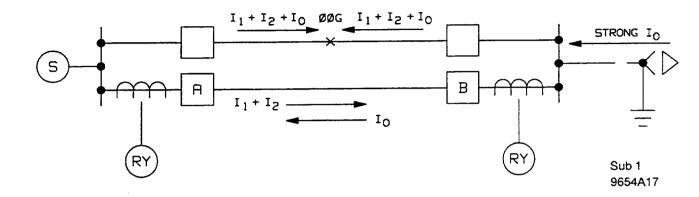

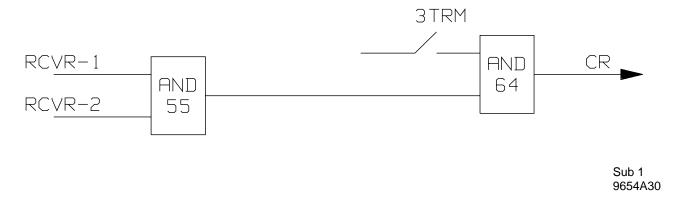

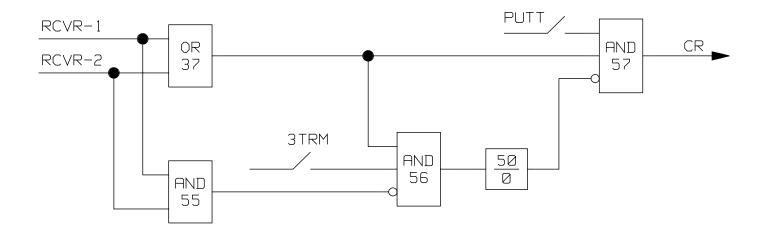

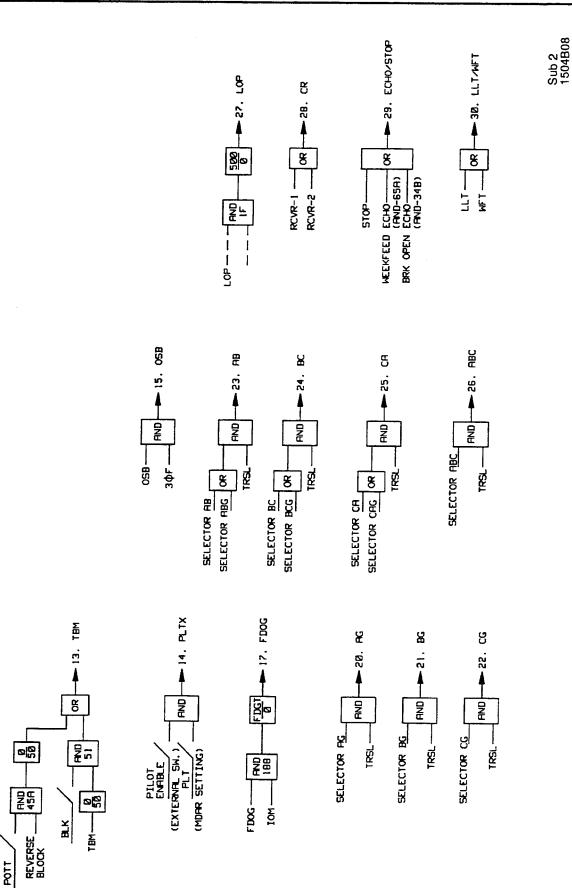

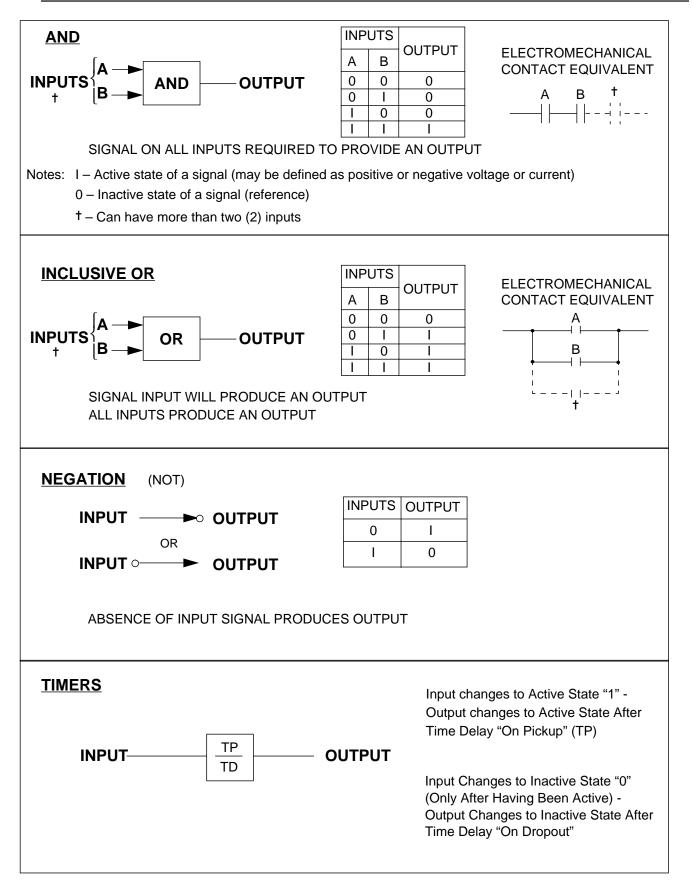

#### 3.4.1 3-Zone Distance Phase and Ground Relay with Reversible Zone-3 Phase and Ground